# The Monolithic-Active-Pixel-Sensor-based vertex Detector (MVTX) Readout and Controls

the technical note for the MVTX readout and controls August 26, 2018 (revision 1.0)

Proposing Organization: Los Alamos National Lab

Principal Investigator: Ming X. Liu

Phone: 505-412-7396 Email: mliu@lanl.gov

Collaborators: Mark Prokop, Alex Tkatchev, Sho Uemura, Kun Liu, Cesar da

Silva, Pat McGaughey, Andi Klein, Xuan Li, Darren McGlinchey,

Sanghoon Lim, Walt Sondheim, Hubert van Hecke

Authors: Alex Tkatchev

Email: alextkatchev17@gmail.com

Sho Uemura

Email: meeg@slac.stanford.edu

# **Todo list**

| completer interface under construction                             | 6   |

|--------------------------------------------------------------------|-----|

| AXI documents. API docs. Linux references. Xilinx docs (DMA, PCIe) | 143 |

# **Table of Contents**

| 1 | Syst | tem Description 1                                        |

|---|------|----------------------------------------------------------|

|   | 1.1  | Description                                              |

| 2 | Sens | sor 4                                                    |

|   | 2.1  | Detector Description                                     |

|   | 2.2  | Stave Description                                        |

|   | 2.3  | ALPIDE Description                                       |

|   |      | 2.3.1 Pulse Injection and Masking                        |

|   |      | 2.3.2 Matrix Readout and Priority Encoder                |

|   |      | 2.3.3 Triggering and Timing                              |

|   |      | 2.3.4 Data Transmission Unit (DTU)                       |

|   |      | 2.3.5 Charge Collection                                  |

|   |      | 2.3.6 Simulation and threshold characterization          |

|   | 2.4  | Interfaces                                               |

|   |      | 2.4.1 Cables                                             |

|   | 2.5  | Power System                                             |

|   | 2.0  | 2.5.1 Specifications                                     |

|   |      | 2.5.1 Specifications                                     |

| 3 | From | nt End Electronics 28                                    |

|   | 3.1  | Description                                              |

|   | 3.2  | Functionality                                            |

|   |      | 3.2.1 GBTx ASIC                                          |

|   |      | 3.2.2 Readout Data Flow                                  |

|   |      | 3.2.3 Trigger                                            |

|   |      | 3.2.4 Wishbone Configuration Bus                         |

|   |      | 3.2.5 Software Configuration Interface                   |

|   |      | 3.2.6 Triple Modular Redundancy (TMR) and Scrubbing      |

|   |      | 3.2.7 Clocking                                           |

|   |      | 3.2.8 Specifications                                     |

|   | 3.3  | Interfaces                                               |

|   |      | 3.3.1 GBT Interface                                      |

|   |      | 3.3.2 I2C Interface to Power Boards                      |

|   |      | 3.3.3 RU interfaces to slow controls                     |

|   |      |                                                          |

| 4 | Bac  | k End Electronics 49                                     |

|   | 4.1  | Description                                              |

|   | 4.2  | GBT wrapper                                              |

|   | 4.3  | Data Processing                                          |

|   | 4.4  | Wupper                                                   |

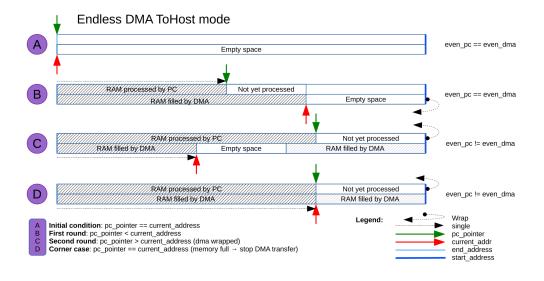

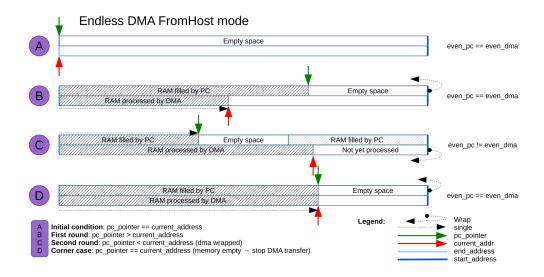

|   |      | 4.4.1 DMA Operation                                      |

|   |      | 4.4.2 Interrupts                                         |

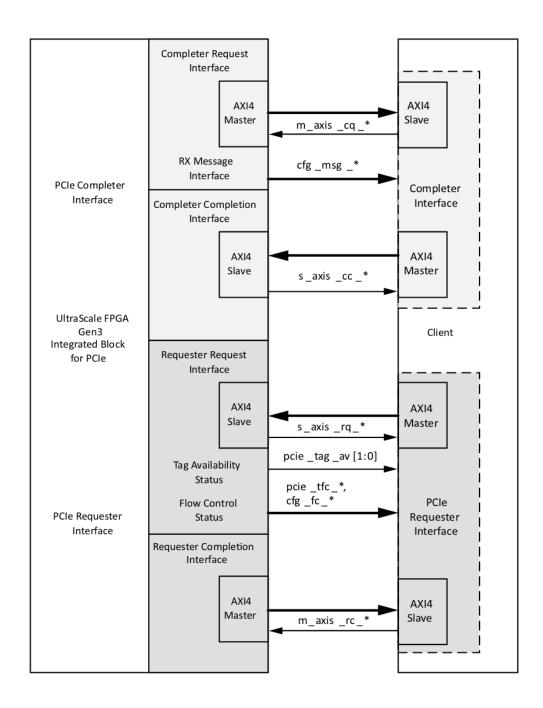

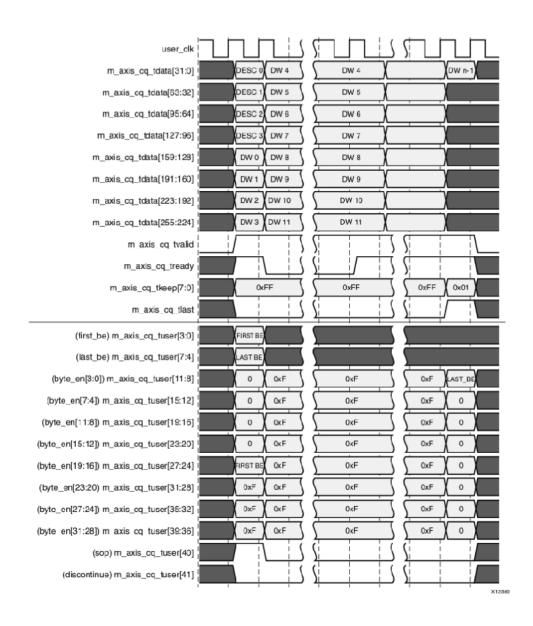

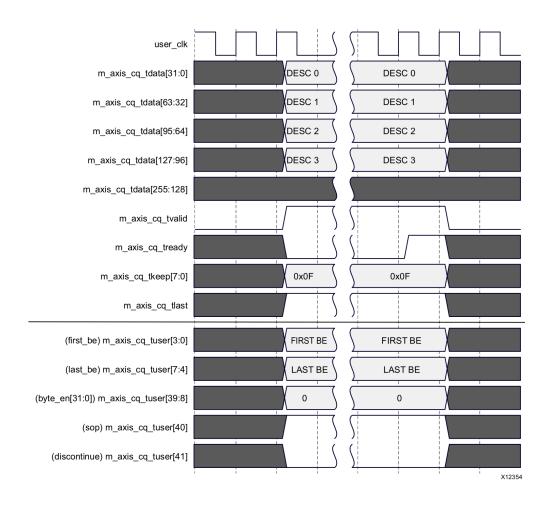

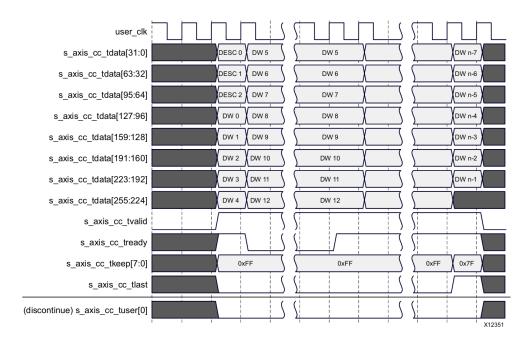

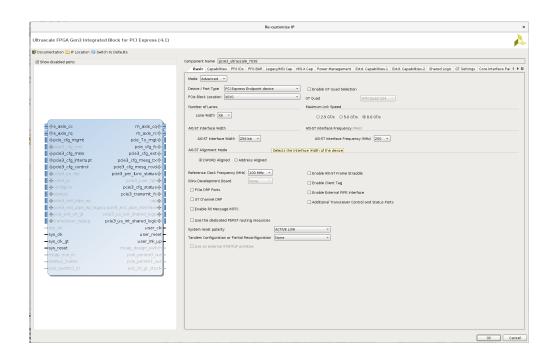

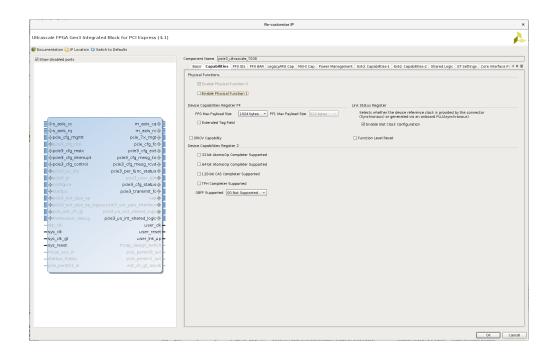

|   |      | 4.4.3 Xilinx PCIe EndPoint Core AXI4-Stream interface 61 |

|   |      | 4.4.4 Firmware Components                                |

|   | 4.5  | Device Drivers                                           |

|   | 4.6  | Register Map                               |

|---|------|--------------------------------------------|

|   | 4.7  | Interfaces                                 |

|   |      | 4.7.1 Fiber Mapping                        |

|   | 4.8  | Hardware                                   |

|   |      | 4.8.1 Clock Distribution and Configuration |

|   | 4.9  | Test and Validation                        |

| 5 | Data | a Acquisition System 98                    |

|   | 5.1  | Description                                |

|   |      | 5.1.1 RCDAQ                                |

|   |      | 5.1.2 FELIX Plugin                         |

|   |      | 5.1.3 Data Format and Decoder              |

|   |      | 5.1.4 Online Monitoring                    |

|   |      | 5.1.5 Offline Analysis                     |

|   | 5.2  | Functionality                              |

|   | 0.2  | 5.2.1 RCDAQ and FELIX Plugin               |

|   |      | 5.2.2 Data Format                          |

|   |      | 5.2.3 Online Monitoring (pmonitor)         |

|   |      | 5.2.4 Offline Software                     |

|   | 5.3  | Interfaces                                 |

|   |      |                                            |

| 6 | Tim  | ing and Triggering                         |

|   | 6.1  | Timing specification                       |

|   | 6.2  | Timing interfaces                          |

|   |      | 6.2.1 Trigger specification                |

|   | 6.3  | Trigger interfaces                         |

| 7 | Con  | trol and Monitoring 111                    |

|   | 7.1  | Description                                |

|   | 7.2  | Functionality                              |

|   |      | 7.2.1 Specifications                       |

|   | 7.3  | Interfaces                                 |

|   | 7.4  | Hardware                                   |

|   | 7.5  | Test and Validation                        |

| 8 | Test | and Validation                             |

| U | 8.1  | Full Chain Test                            |

|   | 0.1  | 8.1.1 FELIX and RCDAQ                      |

|   |      | 8.1.2 RU                                   |

|   | 8.2  | Setup                                      |

|   | 0.2  | 8.2.1 General System Setup                 |

|   |      | 8.2.2 FELIX Firmware                       |

|   |      | 8.2.3 RCDAQ                                |

|   |      | 8.2.4 FELIX Software and Plugin            |

|   |      | <b>C</b>                                   |

|   |      | 8.2.5 Decoder and Online Monitoring        |

|   |      | 0.4.0 IN THIIIWAID AND SULWAID             |

| Aŗ | opendices:                  | 117 |

|----|-----------------------------|-----|

| A  | PCIe                        | 117 |

| В  | AXI                         | 131 |

| C  | PCIe Endpoint Configuration | 132 |

| D  | References                  | 140 |

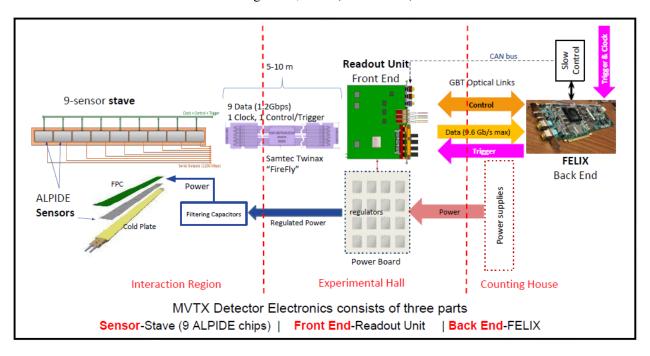

**Figure 1:** Layout of the Maps-based VerTeX detector (MVTX).

# 1 System Description

#### 1.1 Description

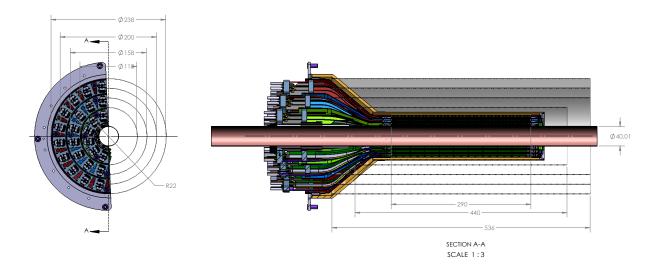

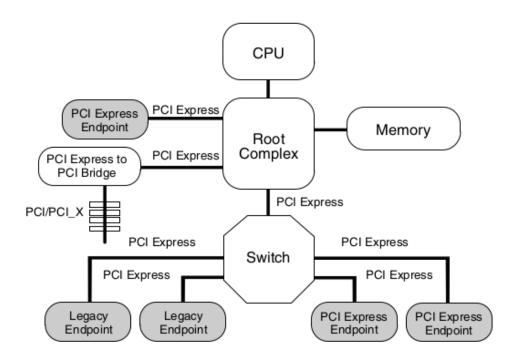

The MVTX design leveraged the R&D performed for the inner layer ALICE/ITS detector described in the technical report [1]. The layout of the MVTX is shown in Figure 1. It consists of the three layers azimuthally segmented in units named staves, which are mechanically independent.

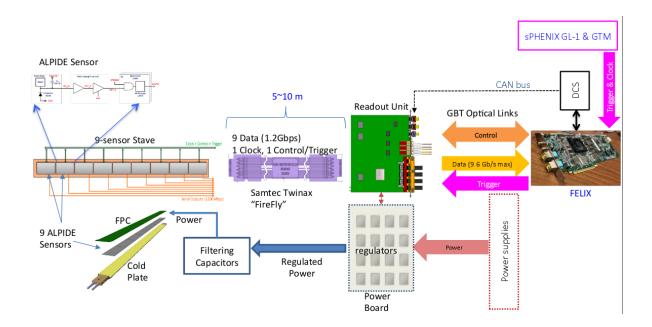

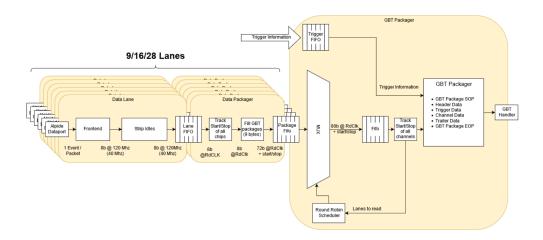

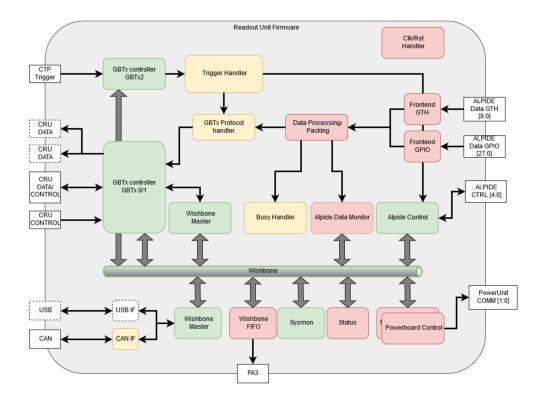

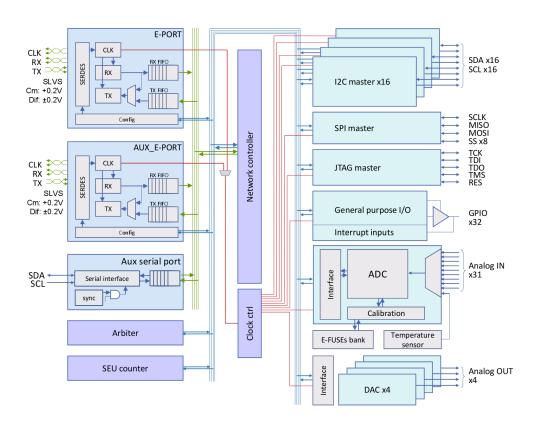

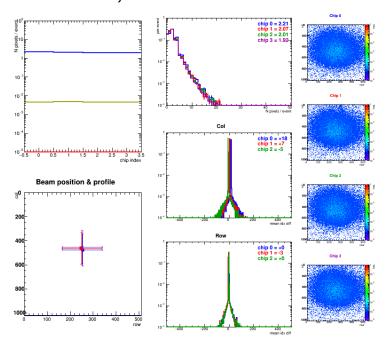

An overview for the whole electronic system is shown in Figure 2. The most fundamental element of the MVTX is the ALPIDE sensor which consists of the pixel matrix, analog frontend, digitization, data formatting, and data transmission integrated in the same chip (monolithic active pixel sensor). Details of the ALPIDE sensor is described in Sec.2.3. Nine ALPIDE sensors are wire bonded to a single Stave with 9 independent data lines and common control and clock.

The nine serialized data links from each Stave is sent to one Readout Unit (RU) trough a 5 meters copper twinax SAMTEC-FireFly cable described in Section 2.4.1. The RU also provides power configuration and monitoring for the Stave. The RU crate is placed outside the sPHENIX magnet area. Details of the RU are described ion Section 3.3. Each RU provides an optical connection to the back-end Front End Link Exchange (FELIX) unit, in the counting house to which the data streams and slow controls are sent trough GBT optical links.

The back-end unit adopted for MVTX is the FELIX board, it has 48 inputs and outputs capable to support GBT optical links over multimode fiber. The board also contains a 16-lane PCIe Gen 3.0 interface to the host server, and a Xilinx Knitex Ultrascale FPGA. One FELIX is expected to support 8 RUs, which

**Table 1:** Geometrical parameters of the MVTX.

|                                          | layer 0   | layer 1           | layer 1   |

|------------------------------------------|-----------|-------------------|-----------|

| Radial position (min) (mm)               | 22.4      | 30.1              | 37.8      |

| Radial position (max) (mm)               | 26.7      | 34.6              | 42.1      |

| Length (sensitive area) (mm)             | 271       | 271               | 271       |

| Pseudo-rapidity coverage                 | $\pm 2.5$ | $\pm 2.3$         | $\pm 2.0$ |

| Active area (cm <sup>2</sup> )           | 421       | 562               | 702       |

| Pixel chip dimensions (mm <sup>2</sup> ) |           | $15 \times 30$    |           |

| Number of chips                          | 108       | 144               | 180       |

| Number of Staves                         | 12        | 16                | 20        |

| Staves overlap in $r\phi$ (mm)           | 2.23      | 2.22              | 2.30      |

| Gap between chips $(\mu m)$              |           | 100               |           |

| Chip dead area in $r\phi$ (mm)           |           | 2                 |           |

| Pixel size (µm)                          | (20 -     | $30) \times (20)$ | ) - 30)   |

will utilize half of the optical links. Each FELIX is installed in a host server. More details on the FELIX board can be found in Section 4.

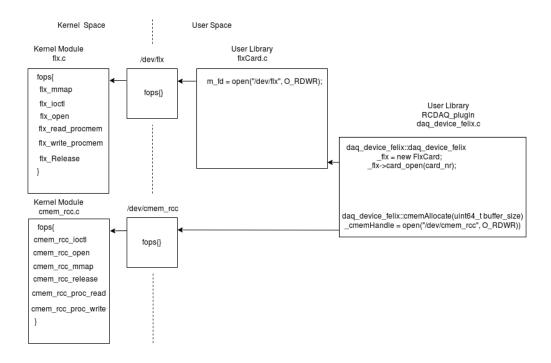

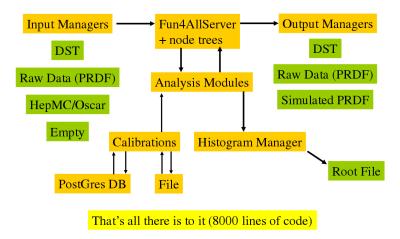

The software running on the FELIX server reads data from FELIX over the PCIe bus, packages it in the sPHENIX data format Phenix Raw Data Format (PRDF), and transfers it to the sPHENIX DAQ. RCDAQ which is the sPHENIX DAQ system is described in Section 5.

The power distribution for the system is performed by the power board, described in Section 2.5. Each Stave is powered by one power board. The Power Boards are supplied by one CAEN bulk power supply. A detail description of the control system is found in Section 7.1.

Details on the signal timing and trigger is described in Section 6.

Figure 2: Block diagram of the MVTX readout electronics.

# 2 Sensor

# 2.1 Detector Description

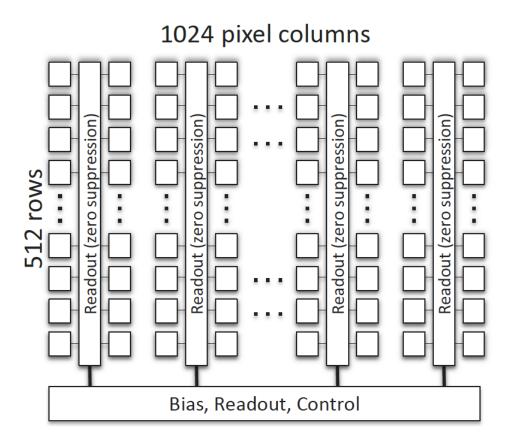

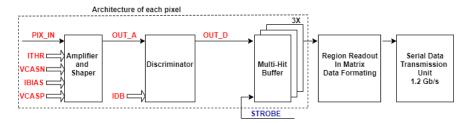

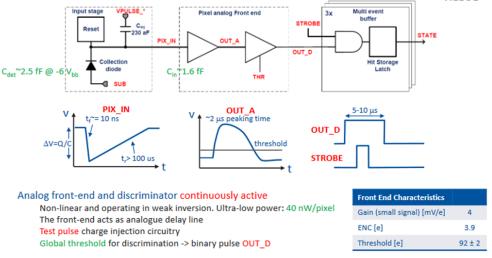

The Stave consists of 9 ALPIDE sensors which takes in a common clock and control line and outputs 9 gigabit data streams. Each ALPIDE sensor consists of a matrix of 512 pixel rows by 1024 pixel columns. Each pixel contains an amplifier discriminator and 3 hit storage multi event buffer. The data output rate is configurable. Zero suppression is done on chip. Readout modes can be configured to triggered or continues mode. The device can be configured for internal pulse injection mode to pulse specific pixels, typically used for testing. PRBS data generation for cable verification. As well as pixel masking functionality in the event a pixel is damaged or remains high. MVTX will use triggered mode at 1.2 Gigs.

## 2.2 Stave Description

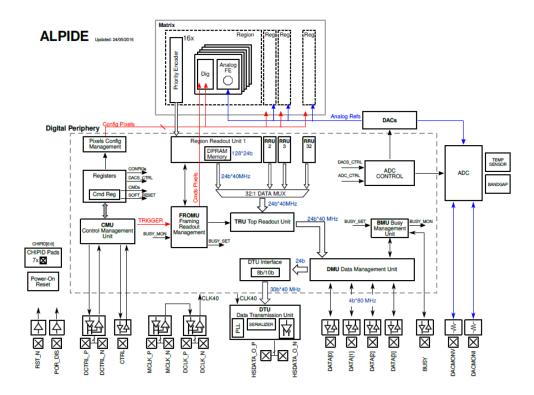

## 2.3 ALPIDE Description

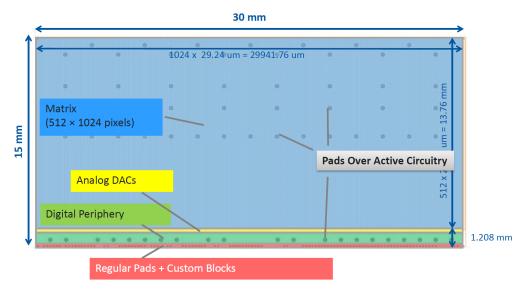

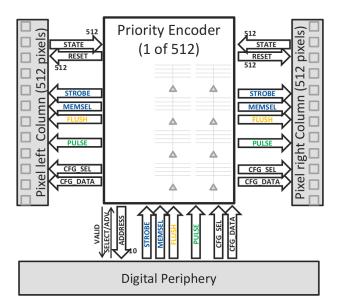

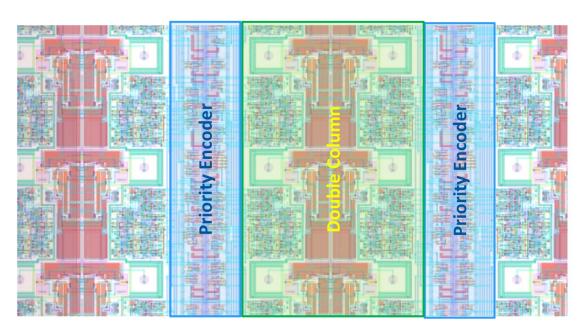

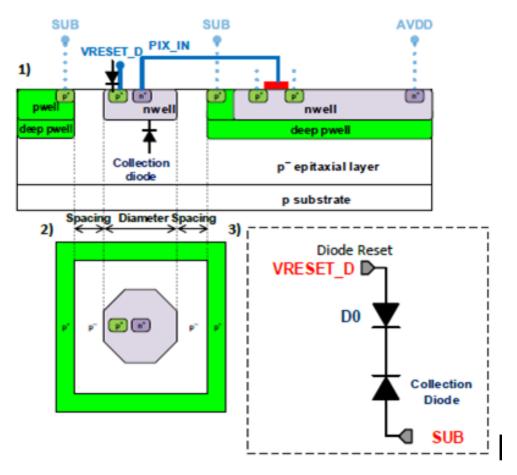

The ALPIDE chip is based on the Monolithic Active Pixel technology implemented in a 180 nm CMOS process fabricated by Tower Jazz. The active pixel region for the ALPIDE sensor is 30mm (X direction) by 15mm (Y direction) which contains  $1024\times512$  (X×Y) sensitive pixels, see Figures 4 and 3. The dimension of each pixel is  $29.24\mu$ m × 26.88  $\mu$ m (X×Y). The pixel columns are counted from 0 to 1023 from left to right along the X axis, and the pixel rows are counted from 0 to 511 from the top to the bottom. The periphery circuit is located in the bottom of the chip within the  $1.2\times30$  mm<sup>2</sup> region.

Figure 3: The ALPIDE sensor Floor Plan.

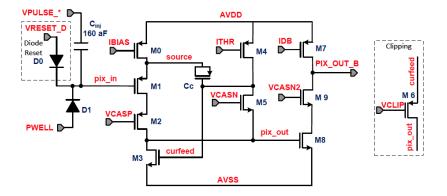

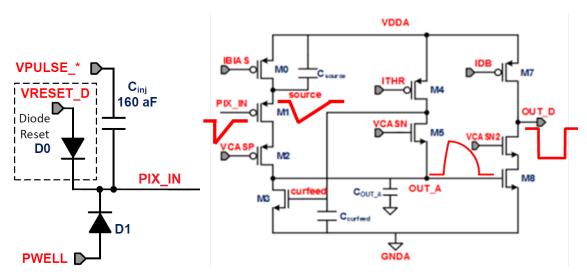

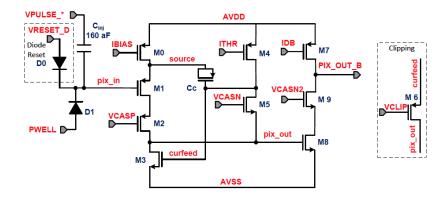

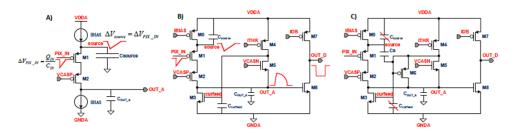

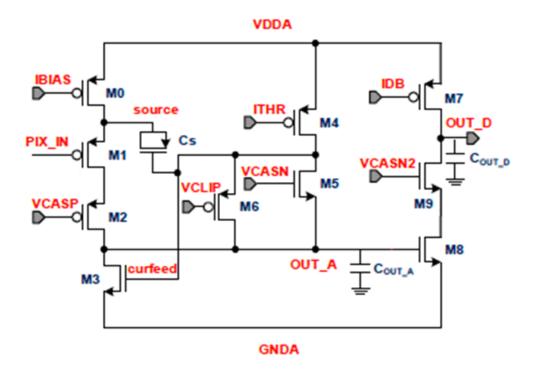

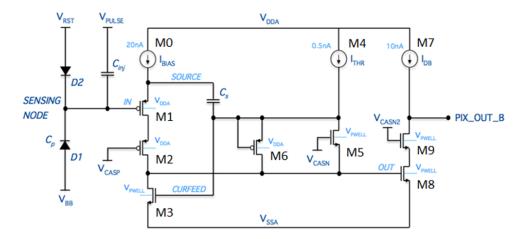

The ALPIDE design is based on a charge sensitive amplifier, amplifier with capacitive feedback. The front-end and discriminator act as an analogue delay line. The readout block diagram is shown in Figure 5 and the schematics is shown in Figure 12. The collection n-well has octagonal shape with 2  $\mu$ m diameter and n-well to p-well spacing of 3  $\mu$ m. In Figure 12, diode D1 is the sensor p-n junction. The input node is continuously reset by diode D0. VRESETD establishes the reset voltage of the charge collecting node (pix\_in). A particle hit will lower the potential at the pixel input pix\_in by a few tens of mV. This will cause the source follower formed by M1 and the current source M0 to force the source node to follow this voltage excursion and dump charge associated with the voltage change and the capacitance of the source node onto

**Figure 4:** The ALPIDE chip architecture.

**Figure 5:** The ALPIDE sensor block diagram.

Figure 6: The ALPIDE front end schematics.

**Figure 7:** The ALPIDE block diagram 2.

Figure 8: The ALPIDE front end schematics.

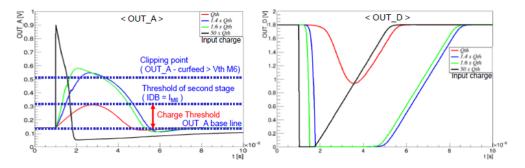

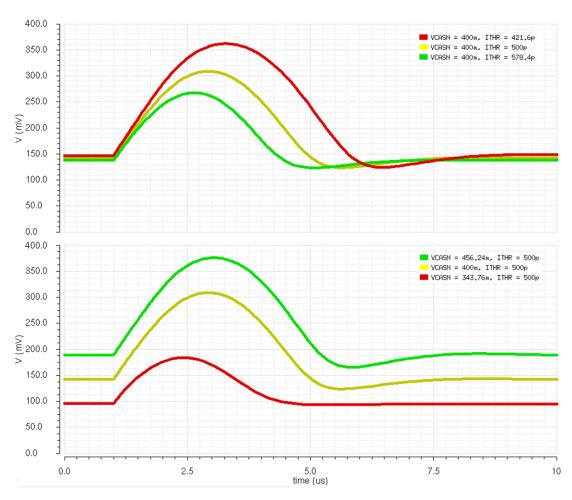

the analog output node pix\_out[2]. The charge threshold of the pixel is defined by ITHR, VCASN and IDB. The effective charge threshold is increased by increasing ITHR or IDB. It is decreased by augmenting VCASN. Voltage bias VCLIP controls the gate of the clipping transistor M6. The lower VCLIP, the sooner the clipping will set in.

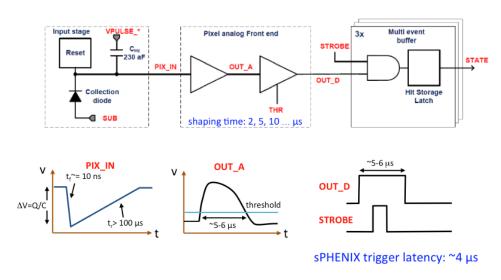

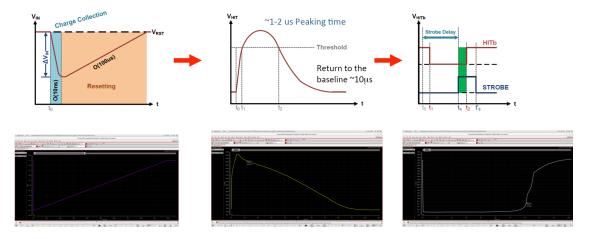

The output of the ALPIDE front-end has a peaking time of around  $2\mu$ s within the typical  $5\mu$ s duration. This allows operating the chip in triggered mode when the latency of the incoming trigger is comparable with the front-end peaking time. A common threshold is applied to all pixels. The latching of the discriminated hits is controlled by global STROBE pulse. The STROBE pulse can be generated from either external trigger or internal trigger, the duration of the STROBE is programmable. Each pixel contains a pulse injection capacitor for the test charge injection in the input of the front-end. A digital-only pulsing mode can be selected to write the logical signal in the pixel memory cells. The pulsing pattern is programmable. The readout of the pixel matrix is based on a circuit named Priority Encoder. The transfer of the matrix data to the periphery circuit is zero-suppressed. The operation voltages are summarized in Table 2.

Each pixel in the ALPIDE matrix has 3 in-pixel data storage elements (buffer). The Multi Event Buffer (MEB) enables the storage of 3 complete frames without the completion of a matrix readout or any data loss.

|                      | Minimum value | Default value | Maximum value |

|----------------------|---------------|---------------|---------------|

| AVSS (Analog ground) | 0 (V)         | 0 (V)         | 0 (V)         |

| AVDD (Analog supply) | 1.62 (V)      | 1.8 (V)       | 1.98 (V)      |

| DVSS (Analog ground) | 0 (V)         | 0 (V)         | 0 (V)         |

| DVDD (Analog supply) | 1.62 (V)      | 1.8 (V)       | 1.98 (V)      |

| PWELL (Bias Voltage) | -6 (V)        | TBD           | 0 (V)         |

| SUB (Bias Voltage)   | -6 (V)        | TBD           | 0 (V)         |

**Table 2:** The operation voltage for the MVTX chip/stave.

The data from the 32 region readout blocks are assembled and formatted by a Top Readout Unit module. There are two readout modes: one is the "Triggered" mode, the other is the "Continuous" mode. The "Triggered" mode defines as the strobe generation and readout are triggered externally. The "Continuous" mode refers to the frames are continuously integrated and readout with programmable strobe duration.

#### 2.3.1 Pulse Injection and Masking

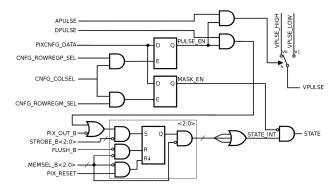

Figure 9: The ALPIDE pixel logic.

The pixels of the ALPIDE chip contain built-in testing features. They can be used to force the generation of a hit using a test charge injection capacitor (analog pulsing), directly setting the pixel state register (digital pulsing), or disabling readout of the pixel (masking). Details on the pixel digital section including pulsing are shown in Figure 9. Each pixel contains two read-only registers: MASK\_EN and PULSE\_EN. The Mask Enable (MASK\_EN) register disables readout of the pixel so the pixel will not report a hit under any circumstance (real particle, analog pulse, or digital pulse). The Pulse Enable (PULSE\_EN) register enables the pulsing functionality of the pixel; this register must be enabled for the pixel to respond to APULSE or DPULSE signals. The MASK\_EN and PULSE\_EN registers for all pixels are controlled through special register writes; individual pixels, or arbitrary patterns of pixels, can be masked or pulsed.

Once the pulsing has been enabled in the desired pixels, two pulsing signals (APULSE and DPULSE) are used to trigger the injection of the charge in the front-end or to set the state register. The edges of the APULSE signal cause the injection of current pulses in the front-end input node pix\_in. The polarity of the pulse depends on the direction of the edge (rising or falling). The rising edge simulates the effect of release of charge in the collection diode by a particle hitting the pixel. The total charge of the current pulse is controllable by dedicated DACs. The DPULSE signal can be used to set the pixel state latches that constitute the Multi-Event buffer. Both pulsing operations require that the PULSE\_EN latches of the target pixels are set and that one of the three global STROBE signals is asserted, in order to store the hit in the corresponding MEB location. The masking of the pixels has priority over the pulsing, therefore a masked pixel does not produce a hit when it is pulsed.

#### 2.3.2 Matrix Readout and Priority Encoder

The readout of pixel hit data from the matrix is based on a circuit named Priority Encoder, depicted in Figure 10. There are 512 instances of this circuit, one every two pixel columns. The Priority Encoder provides to the periphery the address of the first pixel with a hit in its double column, selecting it according to a hardwired topological priority. During one hit transfer cycle a pixel with a hit is selected, its address is generated and transmitted to the periphery and finally the in-pixel memory element is reset. The address of the next pixel with a hit in the double column is then calculated. This cycle is repeated until the addresses of all pixels initially presenting a valid hit at the inputs of a Priority Encoder have been transmitted to the periphery and all the pixel state registers have been reset. The transfer of the frame data from the matrix to the periphery is therefore zero-suppressed.

Each Priority Encoder is a fully combinatorial circuit and it is steered by sequential logic in the periphery during the readout of a matrix frame. It is implemented in a very narrow region between the pixels, extending vertically over the full height of the columns: see Figure 11. There is no free running clock distributed in the matrix and there is no signaling activity if there are no hits to read out. The average energy needed to encode the address of a hit pixel is of the order of 100 pJ. Power is consumed proportionally to the readout rate and to the frame occupancy. The Priority Encoders also implement the buffering and distribution of readout and configuration signals to the pixels.

# 2.3.3 Triggering and Timing

For the MVTX operation at the sPHENIX experiment, we foresee to use the trigger mode as sPHENIX data taking will be mainly in triggered mode(maximum rate = 15 kHz). The collection of pixel states (reffed as frame) will be generated at a particular time and transmitted off chip following the reception of a trigger. The distribution of the MVTX timing and trigger is shown in Figure 13. The sPHENIX level-1 (LV1) trigger latency is around 4  $\mu$ s. This leads to the study of the trigger delay time and ALPIDE pulse shaping time tuning to check any impacts on the efficiency. This trigger latency also raises the question of the pile up effects on the MVTX track efficiency at sPHENIX especially in the several MHz p+p collisions.

Figure 10: The ALPIDE priority encoder.

Figure 11: The layout of the pixel matrix, showing the double columns and priority encoders.

Figure 12: The ALPIDE waveforms.

# **ALPIDE/MAPS Timing & Operation**

Well fit sPHENIX/RHIC environment, 10MHz Clock (LHC 40MHz)

Figure 13: Block diagram of the ALPIDE pixel timing and trigger.

**Figure 14:** The format of the ALPIDE chip transaction on the control bus.

Figure 15: The format of the ALPIDE chip transaction on the control bus.

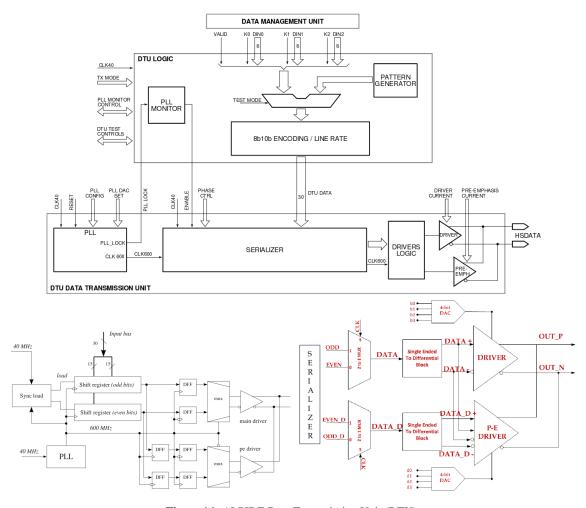

#### 2.3.4 Data Transmission Unit (DTU)

The Data Transmission Unit (DTU) provides a fast serial link for the transmission of the data from the ALPIDE sensor. For MVTX, each sensor's DTU transmits data over a differential serial line with a line rate of 1.2 Gb/s to the off-detector electronics (Readout Unit). The data stream is transmitted over an aluminum over polyimide FPC (Flexible Printed Circuit) and then to a micro-twinaxial cable.

The DTU consists of two modules: a DTU Logic module, which interfaces the ALPIDE's Data Management Unit to the DTU, and the Data Transmission Unit itself, which contains the serializer, the transmission clock PLL, and the LVDS drivers. The DTU Logic module has the following functions:

- 8b/10b encoding of the data produced by the Data Management Unit and to be transmitted by the DTU

- Programming of the serial port line rate (1200 Mb/s, 600 Mb/s, 400 Mb/s) according to operating mode and configuration

- Monitoring of the PLL lock status and re-synchronization of the serializer

- Test features for the Data Transmission Unit: bypass of 8b10b encoding, PRBS-7 pseudorandom pattern, or static test pattern

The Data Transmission Unit and its Serializer are agnostic of the programmed output line rate. They always operate in the same fashion, shifting out a 30 bits data word loaded into the serializer at every cycle of the main digital clock (40 MHz). It is the DTU LOGIC that generates the 30 bits of the DTU DATA bus to obtain the desired output rate, effectively generating slower bit serial stream at the DTU output. For the

operation at 1200 Mb/s, all bits of the DTU DATA bus can be different. When transmitting at 600 Mb/s, every bit is replicated and transmitted twice, or equivalently for two consecutive bit Unit Intervals. Finally, every bit is replicated three times when operating at 400 Mb/s.

The DTU interface is designed to have an output signal compatible with the LVDS standard (at least for the voltage swing; the common mode voltage is reduced to 0.9 V). Resistive termination is required. A 600 MHz transmission clock is provided by an on-chip PLL.

The DTU architecture, shown in Figure 16, is based on a Double Data Rate (DDR) transmission scheme. The DTU Logic module generates a 30-bit word every 40 MHz clock cycle, which is loaded into two 15-bit shift registers. The 1.2 Gb/s line rate, combined with the 8b10b gives a data rate of 960 Mb/s for the MVTX configuration, or 3 bytes per 40 MHz clock cycle. The two shift registers are synchronized on the two 600 MHz clock edges and drive the line driver after a single-ended to differential conversion. A secondary path, equal to the main one but with two extra delay latches drives a second driver in order to provide pre-emphasis.

Figure 16: ALPIDE Data Transmission Unit (DTU).

The LVDS driver provides a current between 0 and 5 mA with a 0.312 mA resolution over a 100  $\omega$  differential cable. The driver is compatible with both commercial LVDS receivers and the GBTX SLVS

receivers. A pre-emphasis current of up to 50% (0 to 2.5 mA) has been implemented in order to be able to compensate for excessive RC on the cable. The pre-emphasis time width is one bit period, i.e. the current bit is emphasized if different from the previous one. The driver and pre-emphasis currents are controlled with 4-bit DACs. The output common mode has been set to 0.9 V (i.e. lower than the 1.2 V from the LVDS standard) in order to reduce the power consumption and have a better match with the 1.8 V supply voltage.

The ALPIDE line rate can be switched between 400 Mb/s, 800 Mb/s, and 1200 Mb/s. This is implemented by repeating the

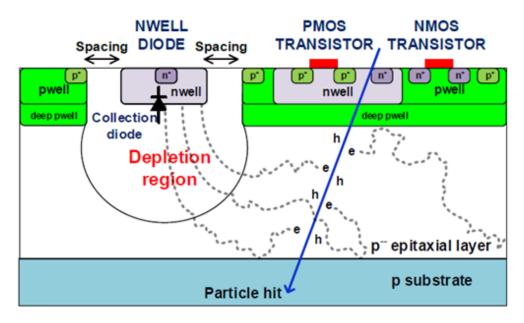

#### 2.3.5 Charge Collection

Figure 17: Depletion Region

When a charged particle passes through the silicon of the ALPIDE sensor, the energy lost by the particle is converted to electron-hole pairs. The signal detected by the ALPIDE consists of free electrons created in the epitaxial layer of the sensor and collected in a collection diode. The epitaxial layer is a layer of high-resistivity, weakly p-type doped silicon, and is bounded below by a p-type substrate and above by a deep p-well. Since both the substrate and p-well are more heavily doped than the epitaxial layer, there is a potential difference that prevents electrons from traveling from the epitaxial region to these others. Except for the collection diode, all of the in-pixel circuitry is contained inside the deep p-well so it cannot interfere with the collection of electrons from the epitaxial layer.

The collection diode is an octagonal n-well implanted in the epitaxial silicon through an opening in the deep p-well: see Figure 20. The p-n junction between the n-well and the epitaxial silicon results in a depletion region devoid of holes in the epitaxial layer, where the concentration gradient of holes (which tends to push holes towards the epitaxial layer) overcomes the electric field created by the charge imbalance in the depletion region (which tends to force holes towards the n-well). The high electric field in the depletion region drifts any electrons inside the depletion region rapidly to the collection diode n-well.

Electrons created in the epitaxial layer cannot enter the substrate or p-well regions, so they diffuse in the low electric field until they hit a depletion region. This diffusion process is slow and random, so electrons can end up in collection diodes far from where the electron-hole pair was created. Applying a reverse bias to

the collection diode by applying a negative voltage to the substrate enlarges the depletion region, increasing the probability that an electron is collected quickly.

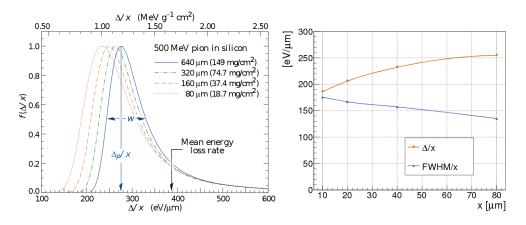

The size of the signal created in the ALPIDE is based on the number of electron-hole pairs created in the epitaxial layer. The epitaxial layer is 25  $\mu$ m thick; as shown in Figure 18 the rate of energy loss by a minimum ionizing particle varies but has a mean value of 388 eV/ $\mu$ m and (for this thickness) a most probable value around 210 eV/ $\mu$ m. The number of electron-hole pairs created is related to the energy deposited by the ionization energy, which for silicon is 3.67 eV. Therefore the mean number of electron-hole pairs is 25  $\mu$ m × 388 eV/ $\mu$ m/3.67 eV = 2600 electrons, and the most probable number is 25  $\mu$ m × 388 eV/ $\mu$ m/3.67 eV = 1400 electrons.

Figure 18: Energy deposition by minimum-ionizing particles in thin silicon.

#### 2.3.6 Simulation and threshold characterization

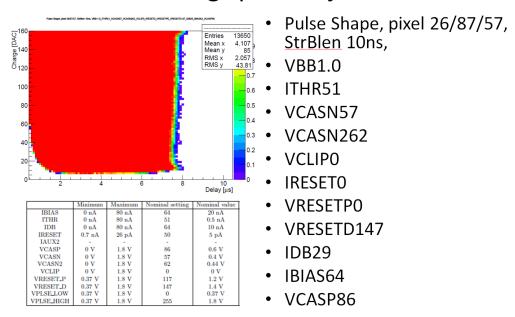

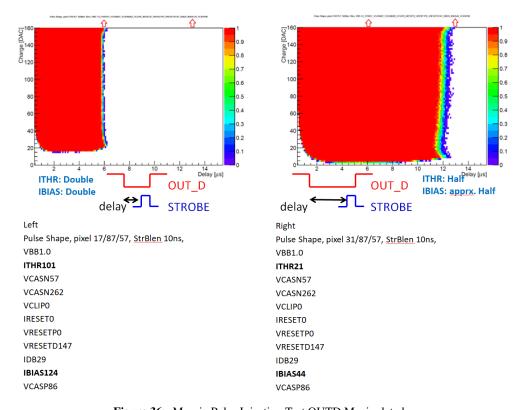

The purpose of this section is to convey a circuit description of the ALPIDE front end, as well as simulate and characterize its bias and threshold parameters IBIAS, ITHR, IDB, VCASP, VCASN, and VCASN2. The effort began by reaching out to Tower Jazz, special thank to Vivian Gin and obtaining the respective PDK (Process Design Kit). A PDK is a model of the devices within a certain technology variation for their processes, typically provided by the foundry to an ASIC design team. After simulating the schematic is Figure8 and presenting it to Thanushan Kugathasan of the ALPIDE design team at CERN, additional suggestions and guidance was provided for a more accurate simulation. The below section could not have been have been completed without help from Vivian Gin and Thanushan Kugathasan our team is forever grateful for their time. This section is divided into three parts Part 1: ALPIDE front end schematic description. Part 2: ALPIDE simulation results and conclusion Part 3: ALPIDE laser test stand results.

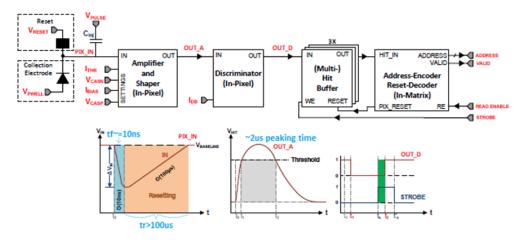

The architecture of each ALPIDE pixel contains a sensing diode, amplifier and shaper stage, discriminator stage, and a digital section consisting of three hit storage registers (Multi Event Buffer). The latching of the discriminated signal above a threshold by the multi-hit buffer is controlled by three global STROBE signal. Once the signal is latched the Address- Encoder Reset-Decoder (AERD) provides the ADDRESS of the hit pixel and whether the current address is VALID to the chip periphery containing the DTU (Data Transmission Unit). The data is then sent off chip at 1.2Gbps (Inner Barrel). The description below will reference the three stages and the input signals of each stage PIX\_IN, OUT\_A, and OUT\_D.

The voltage at the input node PIX\_IN drops within the charge-collection time below 10 ns. The reset mechanism lets PIX\_IN return to the baseline voltage VBASELINE in about 100 us. The signal amplified

Figure 19: Simulation ALPIDE Reference.

by the front-end that acts as a delay line with a peaking time of around 2 us, the discriminated pulse pulse has an approximate duration of less than 10 us.

The reset is provided either by a diode or a PMOS. The PMOS-reset is a constant-current reset mechanism which provides the current IRESET when VIN deviates from the baseline value. The reset current IRESET can be adjusted to achieve the desired reset time and to adapt to the leakage current of the pixel. The baseline of the pixel can be regulated using VRESET. The diode reset is based on a single forward-biased diode.

The amplifier and shaper consist of two current branches, IBIAS (transistor M0) and ITHR (transistor M4). It receives the input signal PIX\_IN and manipulates it in accordance with the IBIAS, ITHR, VCASP, VCASN, and bias and threshold parameters then outputs the OUT\_A signal to the discriminator stage. The discriminator stage discriminates and inverts the analog input OUT\_A to a digital active low output pulse OUT\_D in accordance with the IDB threshold parameter.

Without external stimulation the input transistor M1 conducts the current IBIAS provided by the current source M0. The transistor M5 conducts ITHR current provided by the current source transistor M4, leading to a fixed voltage difference on OUT\_A and VCASN. VCASN is used to define the baseline voltage of OUT\_A after a particle hit. The cascode transistor M2 transistor circumvents the Miller effect for the input transistor.

Transistors M4 and M5 are used to generate a low frequency feedback to adjust conductivity since all transistors operate in the weak inversions region. The curfeed net loaded with Ccurfeed capacitance is connected to gate of transistor M3. The transistor M3 absorbs IBIAS+ITHR current. Csource and Ccurfeed are combined in one capacitance Cs as shown in figure Figure 21 C.

The source of M1 is coupled to the current-feedback node Ccurfeed. The capacitance of M1 input is much larger than the capacitance of OUT\_A. Therefore, the concept is based on charge transfer from a large capacitance to a small capacitance to generate a voltage gain. When PIX\_IN receives a negative input pulse, the voltage drop at the gate of M1 increases its current which flows between M1 and OUT\_A. With some delay Vsource node and Vcurfeed follow PIX\_IN, leading to reduced conductivity of M3 and OUT\_A increases. The increase in OUT\_A allows M5 to close. Therefore, ITHR charges Cs leading to an increase in Vcurfeed and increases conductivity of M3.

The transistor M6 serves as a clipping mechanism once OUT\_A exceeds Vcurfeed and as a pulse dura-

Figure 20: Diode Reset.

tion compressor. Transistor M6 in a diode connection: source and gate are connected to the curfeed node and the drain is connected to the OUT\_A node. Normally M6 is reverse biased, but when the OUT\_A signal is high enough to forward bias it, M6 provides additional discharge current to compress the pulse duration. The clipping effect is noticeable for input charges larger than 1.4 times the charge threshold both for OUT\_A and OUT\_D. The rise time of the pulse is defined by the time ITHR and IBIAS need to charge the OUT\_A node. Additional charge stored at the source node speeds up process. The pulse duration depends on the clipping point and how quickly CURFEED is charged up to increase the conductivity of M3.

Voltage bias VCLIP controls the gate of the clipping transistor M6. The lower VCLIP, the sooner the clipping will set in.

Transistors M7 and M8 form the second stage which discriminates and inverts the OUT\_A signal. In static operations the output current is almost zero however once OUT\_A is present it increases the transconductance of M8 and the node OUT\_D is discharged. The cascode transistor M9 shown in figure 21 was added to reduce the equivalent Miller capacitance on pix out.

Figure 21: ALPIDE Front End Schematic Principle Practical Implementation Presented Circuit

Figure 25 shows C\_in=1.6 fF. 5e3 elementary charge / 1.6e-15 farad = 0.5 V.

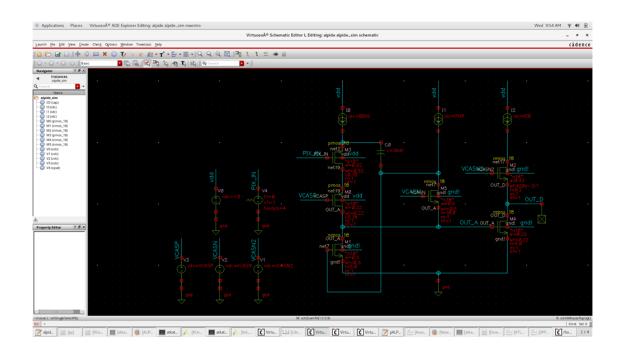

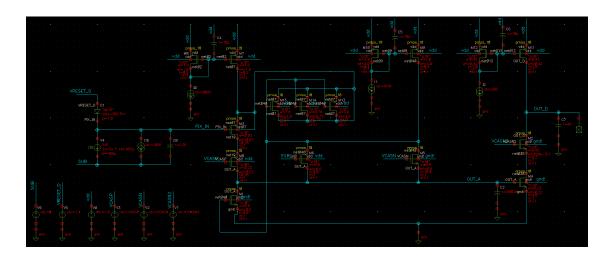

Transistors M0, M4, and M7 have been replaced with variable current sources as shown in figure 26 which are controlled in maestro tab using ADE Explorer (virtuoso simulation environment). The voltage parameters VCASP, VCASN and VCASN2 are also variable and controlled in the maestro tab. figure 27 shows the initial simulation schematic following the reference.

The initial simulation schematic was later modified to obtain a more accurate simulation result. The current sources were replaced with current mirrors. The reset circuit was added and the cc capacitor was more accurately modeled with the transistor array shown in 28.

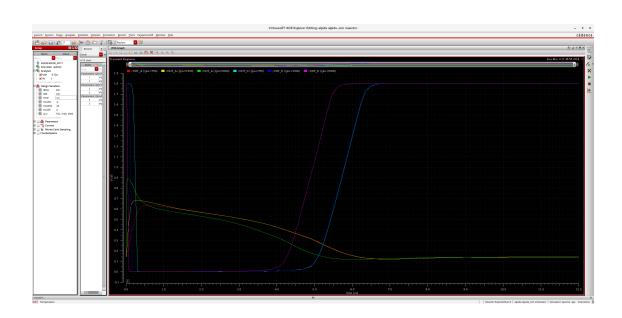

Figure 29 shows the default threshold parameters as shown in the ALPIDE Manual and 30 shows OUT\_A and OUT\_D using the defaults. Please observe the bias and threshold parameters appear to the left of every waveform displayed.

The waveforms in 30 show OUT\_A and OUT\_D with 750 electrons, 1550 electrons, and 5000 electrons at the input. The figures in 31 and 32 show variation of the threshold parameters showing a change in OUT\_A and OUT\_D. Please observe the bias and threshold parameters appear to the left of every waveform displayed.

#### 2.4 Interfaces

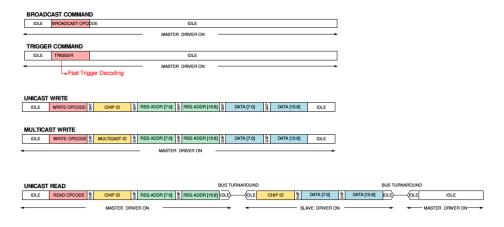

The ALPIDE chip has custom control interfaces. The differential control port (DCTRL) supports bidirectional serial signaling at 40 Mb/s. A second single ended control line (CNTRL) is also available but is not used for MVTX. The nine sensors on the MVTX stave are directly connected to a shared control differential line using the DCTRL port. The Control Management Unit block implements the control layer

Figure 22: ALPIDE Optimized Schematic

|         | M0      | M1        | M2        | М3    | M4    | M5     | M6    | M7     | M8     | M9       | Cs     |

|---------|---------|-----------|-----------|-------|-------|--------|-------|--------|--------|----------|--------|

| W/L     | 1.8/8.5 | 0.92/0.18 | 0.22/0.18 | 0.5/5 | 2/8.4 | 0.5/10 | 0.5/3 | 0.42/7 | 0.22/4 | 0.42/0.2 | 344 fF |

| [um/um] |         |           |           |       |       |        |       |        |        |          |        |

Figure 23: Transistor Sizes Table

Figure 24: ALPIDE Transient plots OUT\_A OUT\_D from Presentations and papers

#### Digital pixel circuitry with three hit storage registers (multi event buffer)

Global shutter (STROBE) latches the discriminated hits in next available register In-Pixel masking logic

Figure 25: ALPIDE Capacitance

Figure 26: ALPIDE Simulation Schematic reference.PNG

Figure 27: ALPIDE Simulation initial

Figure 28: ALPIDE Simulation Schematic.PNG

|            | Minimum           | Maximum | Nominal setting | Nominal value      |

|------------|-------------------|---------|-----------------|--------------------|

| IBIAS      | 0 nA              | 80 nA   | 64              | 20 nA              |

| ITHR       | 0  nA             | 80 nA   | 51              | 0.5  nA            |

| IDB        | 0  nA             | 80 nA   | 64              | 10 nA              |

| IRESET     | 0.7  nA           | 26 pA   | 50              | 5  pA              |

| IAUX2      | -                 | -       | -               | -                  |

| VCASP      | 0 V               | 1.8 V   | 86              | 0.6 V              |

| VCASN      | 0 V               | 1.8 V   | 57              | $0.4 \mathrm{\ V}$ |

| VCASN2     | 0 V               | 1.8 V   | 62              | $0.44~\mathrm{V}$  |

| VCLIP      | 0 V               | 1.8 V   | 0               | 0 V                |

| VRESET_P   | $0.37~\mathrm{V}$ | 1.8 V   | 117             | 1.2 V              |

| VRESET_D   | $0.37~\mathrm{V}$ | 1.8 V   | 147             | $1.4~\mathrm{V}$   |

| VPLSE_LOW  | $0.37~\mathrm{V}$ | 1.8 V   | 0               | 0.37  V            |

| VPLSE_HIGH | 0.37 V            | 1.8 V   | 255             | 1.8 V              |

Table 4.2: DACs specifications overview.

Figure 29: Default threshold parameters from ALPIDE manual

Figure 30: ALPIDE Simulation threshold parameters at defaults OUT\_A and OUT\_D with 750 1550 5000

Figure 31: ALPIDE Simulation threshold parameters to get to 8us OUT\_A and OUT\_D with 750 1550 5000

Figure 32: ALPIDE Simulation threshold parameters to get to 8us 2 OUT\_A and OUT\_D with 750 1550 5000

Figure 33: Simulation Validation

Figure 34: Threshold Parameters

# Default settings pulse injections test

Figure 35: Mosaic Pulse Injection Test

Figure 36: Mosaic Pulse Injection Test OUTD Manipulated

and provides full access to the control and status registers of the chip. The DCTRL and DCLK differential ports are implemented with a custom designed differential transceiver cell. This has been designed with reference to the standard TIA/EIA-899 Electrical Characteristics of Multi-point-Low-Voltage-Differential-Signaling (M-LVDS). The control bus can used to distribute commands to the chip, mostly on the trigger messages. The format of the transaction on the control bus has been shown in Figure 14.

All the analog signals are generated by a set of on-chip 8 bit DACs. The analog section of the periphery also contains an ADC with 10-bit dynamic range, a bandgap voltage reference and a temperature sensing circuit. The ADC can used to monitor the outputs of the DACS, the analog and digital supply voltages, the bandgap voltage and the temperature.

The Data Transmission Unit (DTU) provides a fast serial link for the transmission of the data from the ALPIDE. The MVTX chip transmits its data over a differential serial line with a line rate of 1.2 Gb/s to the off-detector electronics (such as the Readout Unit or the MOSAIC readout module). The data stream is transmitted over an aluminum over kapton FPC (Flexible Printed Circuit) with a maximum length of 300 mm and then to a micro-coaxial cable over a length of 5 m (can be tuned to 7m or 10m based on the sPHENIX integration study).

The power dissipated by the pixel chip shall not exceed 300 mWcm<sup>-2</sup>. The power consumption is less than 40 mW/cm<sup>2</sup> measured in operating condition.

#### **2.4.1** Cables

SAMTEC DESC OF NEW CABLES

## 2.5 Power System

#### 2.5.1 Specifications

Figure 37: Power supply system for MVTX.

The power for the entire MVTX system (Fig. 37) is supplied by:

• one CAEN EASY3000 crate

- one A1676A EASY Branch Controller

- two A2518 LV 8V 10A (50W) modules

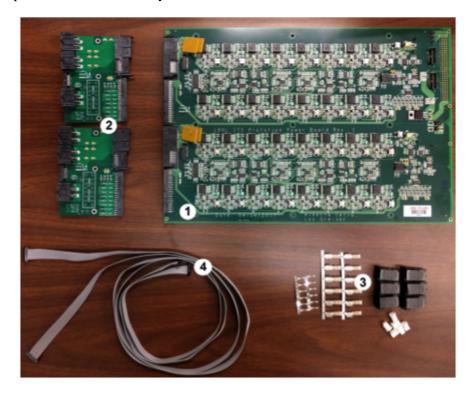

The system can supply 64 channels, even though MVTX will need only 48 power channels, one channel per power board/RU/stave. The CAEN crate uses one CAEN Power supply (TBD, SY8800?, A3484/5/6). The power board (Fig.38) has 32 controllable channels for each RU/stave unity. (Needs more specs for the power boards. Operation, interfacing, controls, what are the numbers in the figure? etc...Cesar) The power system will be part of the slow control system.

Figure 38: Power card for one Readout Unity/Stave.

1mega hit per mm squared kilahit per cm squared negative bias gives a better depletion ithr vcasn

# 3 Front End Electronics

## 3.1 Description

The RU is the frontend board for MVTX.

## 3.2 Functionality

#### 3.2.1 GBTx ASIC

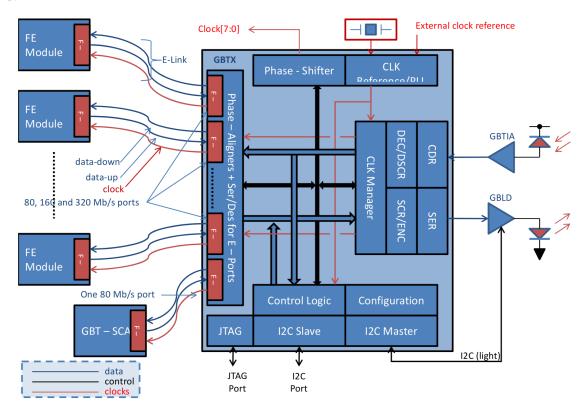

The optical GBT link between the RU and FELIX is the main interface between the RU and the counting house. On the RU, the link is implemented with two components: the VTRx/VTTx optical module and the GBTx ASIC. The VTRx and VTTx are SFP-like modules designed by CERN for high radiation tolerance. The GBTx is the hardware implementation of the GBT protocol; Figure 39 shows the functionality of the ASIC.

Figure 39: GBTx architecture and interfaces.

The GBTx configuration registers can be set in several ways. First, they can be accessed over the GBTx I2C slave interface; on the RU this is connected to an I2C master firmware block in the Kintex Ultrascale FPGA, so the GBTx can be configured through the FPGA's Wishbone bus (further described in Section 3.2.4. Second, the registers can be accessed through the GBT link, as described in Section 3.3.1. Third, the GBTx contains "e-fuses" that can be irreversibly programmed (using a special CERN I2C dongle), so the programmed register values are automatically loaded on power-on.

The GBTx data input and output "e-links" are connected to the Kintex Ultrascale FPGA. The data frame is 80 bits wide and clocked at 40 MHz; on the RU the e-links are configured so the frame is carried on 10 e-links. Each e-link is a differential pair carrying 8 bits of the data frame, serialized at 320 Mbps.

In the FPGA, the serialization and descrialization of the e-links are performed in the gbtx\_controller firmware block. The data to be transmitted is serialized using the Xilinx OSERDESE3 primitive. The data received from the GBTx is descrialized using the Xilinx IDELAYE3 primitive (for fine adjustment of the data alignment with clock) and the ISERDESE3 primitive (descrializer), then passes through a BitSlipInLogic\_8b block (based on Xilinx XAPP1208, to replace similar functionality in the 7-Series ISERDES) that corrects the word alignment of the descrialized data.

#### 3.2.2 Readout Data Flow

Figure 40 shows the data path inside the FPGA from the ALPIDE to the GBTx ASICs. The differential signals from the ALPIDE data port are received by the GTH transceiver on the FPGA. The complete readout flow, from the transceiver to the packaging of the event for transmission over GBT, is contained in the datapath\_ib firmware block, the components of which are described below. All data signals are clocked at the same 160 MHz clock.

**alpide\_frontend\_gth**: This is a wrapper containing the Xilinx transceiver IP core, which handles comma alignment and 8b/10b decoding, and a FIFO that synchronizes the decoded data to the 160 MHz readout clock. The output from this block to the next is the raw (commas and IDLEs not suppressed) ALPIDE data stream (8 bits wide), plus flags for valid (not comma and FIFO not empty) and 8b10b errors.

**alpide\_datapath**: This block performs two functions. First, a protocol\_checker block monitors the incoming data stream and checks for all possible violations of the ALPIDE protocol; the protocol error signals from this block are counted by a alpide\_datapath\_monitor block in datapath\_ib. Second, a protocol\_tracker block identifies BUSY words and only writes valid, non-BUSY words to a FIFO. The interface from this block to the next is the read interface to the FIFO (8 bits wide, clocked at 160 MHz).

data\_packager: This block takes the idle-suppressed bytes from alpide\_datapath and packs them into 72-bit (9 bytes) words for GBT transmission. The interface from this block to the next is a FIFO-like interface (data and valid outputs, read input) with behavior similar to a first-word fall-through FIFO. In addition, three output signals (start, stop, timeout) indicate the data stream state: whether the protocol tracker has detected a start, stop, or timeout in the current event. These signals stay high once asserted and are reset at the end of the event.

gbt\_packer: This block is triplicated (TMR). In addition to the ALPIDE data interface from data\_packager, this block reads the trigger information FIFO in trigger\_handler. When trigger information is received, gbt\_packer waits for data from the data\_packager blocks. When data appears, gbt\_packer transmits the event headers defined by the RU event format, then the data. Since data appears on all active data\_packager blocks, the gbt\_packer arbitrates between data\_packager blocks: on each clock, it reads and transmits a data word from one data\_packager, strobes the data\_packager read line, then selects the next data\_packager that is unmasked, has data (valid asserted), and has not yet sent the end of its event (stop not asserted). Once a stop has been received from every data\_packager, gbt\_packer transmits the event trailer.

**GBT output FIFO**: The output of gbt\_packer is written to a FIFO that is instantiated in datapath\_ib. The read interface of this FIFO is the interface from datapath\_ib to the GBTx controller's TX interface.

#### 3.2.3 Trigger

The RU can operate in two trigger modes: triggered or continuous mode. In triggered mode, the RU sends triggers to the ALPIDE sensors in response to triggers received on the GBT link. In continuous mode, the RU generates triggers on a fixed period. MVTX will use triggered mode.

**Figure 40:** Block diagram of the data flow inside the RU. For MVTX, there are 9 lanes per stave, and the data lanes run at 120 MHz. This diagram corresponds to the datapath\_ib block in the RU firmware. The mapping from diagram blocks to firmware is as follows: Inside "Data Lane," "Frontend" is alpide\_frontend\_gth and "Strip Idles" and the "Lane FIFO" are contained within alpide\_datapath. "Data Packager" is data\_packager. "GBT Packager" is gbt\_packer.

The trigger processing functions are contained in the trigger\_handler block in the Kintex Ultrascale FPGA firmware. This block takes the GBT RX signals as input. The important output interfaces are pulse and trigger signals, which command the ALPIDE control interface to pulse or trigger the ALPIDE sensors, and a trigger FIFO, which commands the readout path to prepare for data and communicates the trigger information that needs to be included in the event data.

The functionality of trigger\_handler is divided among the following components:

- trigger\_handler\_mode\_tracker: set the trigger mode by watching GBT RX for special control words (SOT, SOC, EOT, EOC start/end of triggered/continuous).

- trigger\_handler\_period\_counter: for continuous mode, counts time since last trigger

- trigger\_handler\_distance\_counter: watches ALPIDE trigger line and reports whether the time since last trigger is less than a minimum value (for suppressing close-together triggers)

- trigger\_handler\_generate\_trigger: generates a trigger pulse: for triggered mode, send a trigger

if GBT RX receives a physics trigger, previous trigger was not within minimum distance, and trigger

is not gated

- trigger\_handler\_output\_data: stuffs the trigger FIFO with information about the triggers issued

- pulse\_transfer: widen the output pulse of trigger\_handler\_generate\_trigger from a single 160 MHz clock to 4 clocks

#### 3.2.4 Wishbone Configuration Bus

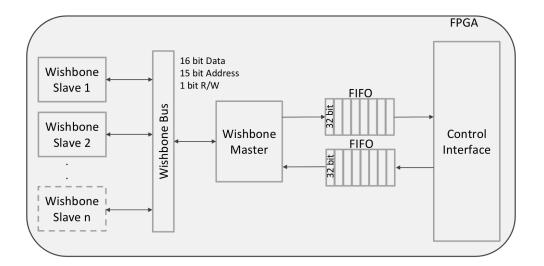

The configuration of the Kintex Ultrascale FPGA is managed using Wishbone, an open-source bus interface. As implemented on the Kintex Ultrascale, the bus is 32 bits wide to match the width of the interface to the Cypress FX3 USB ASIC. Various firmware blocks on the FPGA connect to the shared Wishbone bus. Each such block has a Wishbone module address, and a number of 16-bit Wishbone registers. Figure 42 shows how the addresses and data are packed into a bus transaction.

Figure 41: Block diagram of the Wishbone bus on the RU. The control interface can be either the USB or GBT interface of the RU.

#### DCS -> FPGA • Write Request: Module Addr[6:0] Reg Addr[7:0] Data[15:0] W/R=1 Read Request: W/R=0 | Module Addr[6:0] Reg Addr[7:0] Don't Care[15:0] FPGA -> DCS • Write Response: None (no acknowledgement, but errors are kept in a wishbone slave register – associated with the wishbone master - for possible later interrogation) Read Response: Errors are kept in a wishbone slave register – associated with the wishbone master - for possible later interrogation Module Addr[6:0] Reg Addr[7:0] Data Response[15:0] Error

**Figure 42:** Transactions on the Wishbone bus. Here DCS (Detector Control System) represents the slow control system, and can refer to either the USB or GBT Wishbone masters. The 32-bit bus accommodates a read/write flag, the address of the Wishbone module, the address of the register inside that module, and the 16-bit value of the register.

The Wishbone bus has two "bus masters" that can send read and write commands. The first is accessed through the USB interface on the RU. The second is accessed through the optical GBT interface: special Single Word Transactions (SWT)" are recognized by the GBT controller block in the firmware and interpreted as Wishbone commands.

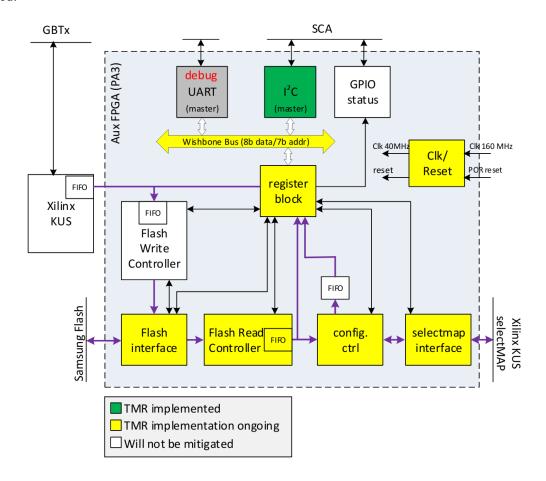

The ProASIC3 FPGA also uses a Wishbone bus for configuration, but the bus is 15 bits wide (7-bit address, 8-bit data) to match the I2C protocol. The ProASIC3 Wishbone bus has two bus masters: one is controlled by the GBT-SCA ASIC through I2C, and the other is controlled through a UART interface.

# 3.2.5 Software Configuration Interface

The RU configuration and monitoring software is implemented in Python. The software interface is used primarily in a regression script (for exercising the system in an automated way) and a testbench (which provides command-line interfaces for setup and test of specific parts of the system). The main building blocks of the software interface are the RU software modules and the communication servers.

Each RU software module corresponds to a Wishbone module inside the RU. The source files for software modules are in the directory modules/board\_support\_software/software/py. Each software module is a subclass of Wishbone Module, which is a class providing generic read and write methods for accessing Wishbone registers for the module. The software modules add module-specific functions that abstract away the register addresses; for example, to select the mask that determines which ALPIDE clock lines are driven by the ALPIDE controller module (register address 0x15), one can call Dctrl.set\_dclk\_mask(value) instead of WishboneModule.write(0x15,value). Modules can also add more sophisticated methods: for example Dctrl.write\_chip\_reg(address, data, chipid) performs the full series of Wishbone writes necessary to command the ALPIDE controller to write a specified register on an ALPIDE sensor.

The RU is represented in software by the class RUv1 (a subclass of ReadoutBoard), which collects the full set of modules that exist in the RU firmware. This class also holds the mapping between ALPIDE sensors and control ports.

The communication servers are Python classes that represent different physical interfaces by which the software can communicate with the RU. Communication servers exist for both the USB interface and the SystemVerilog simulation. For the USB interface, two implementations exist: PyUsbComm, using the PyUSB Python library, and NetUsbComm, which communicates over the network to a C++ implementation of the USB communication (UsbCommServer) using the libusb library. For the simulation, there are two communication servers: UsbCommSim, which simulates the USB interface, and Wb2GbtxComm, which simulates the GBT optical interface. Both communicate with the simulation through buffer files, each of which represents a one-way communications link: the communication server writes (or reads) the file, and the simulation reads (or writes).

The testbench script (software/py/testbench.py) uses Python Fire to generate a command-line interface. Commands in common use include initialize\_boards, setup\_sensors, and setup\_readout.

#### 3.2.6 Triple Modular Redundancy (TMR) and Scrubbing

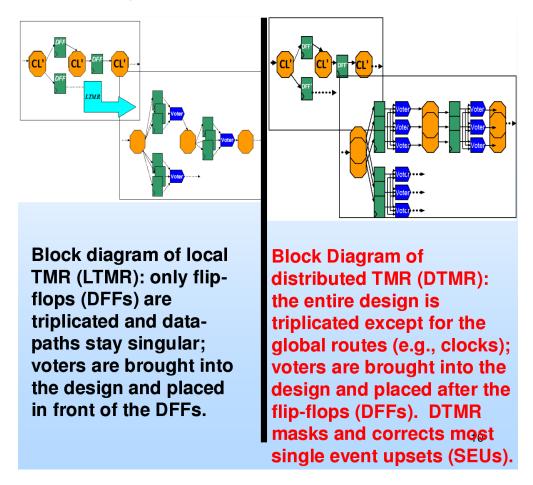

The RU will operate in a radiation environment that can induce single event upsets (SEUs) in configuration memory, flip-flops, and combinatorial logic. A three-part strategy is used to protect the RU logic from these effects.

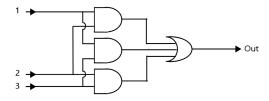

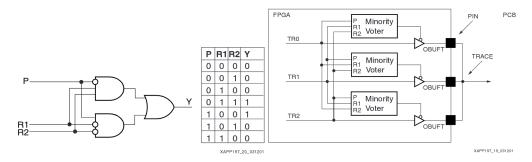

First, the Kintex Ultrascale firmware implements triple modular redundancy (TMR) in many of the logic blocks. TMR in the Kintex Ultrascale firmware is implemented using distributed TMR as shown in Figure 43. Sections of logic to be TMR-ed are divided into blocks consisting of combinatorial logic followed by registered outputs (no internal feedback paths). These blocks are triplicated, and the outputs are processed by triplicated majority voter circuits. As shwon in Figure 44, a majority voter is a combinatorial logic circuit

whose output follows the majority of the inputs: if one input signal is incorrect due to SEU, the output will follow the unaffected inputs and therefore will still be correct. An SEU affecting one of the triplicated blocks is ignored by the voters (since the other two blocks are operating correctly); similarly an SEU affecting one of the three voters is ignored by the voters of the next logic block. An SEU affecting a flip-flop or logic in one triplicated block will clear itself when the affected data is dropped by the voters; since there are no internal feedback paths, bad data cannot survive in the system longer than the propagation delay from one set of voters to the next. SEUs in the configuration only affect the system function if two of the triplicated blocks are affected; to avoid system failure, the first SEU must be corrected before the second SEU occurs.

Figure 43: The two types of triple modular redundancy implemented on the RU.

The majority voter circuit has two identical "mismatch" outputs that indicate when any of the voter inputs disagree with the voter output. The mismatch outputs from all majority voters are read by a radiation\_monitor module, which counts the mismatches and can be read out over the Wishbone bus. This allows real-time monitoring of the SEUs seen on the Kintex Ultrascale FPGA.

Not all of the Kintex Ultrascale firmware is protected by TMR; Figure 45 shows the status of TMR protection of different firmware blocks. Certain firmware blocks, which have relatively low cross-section for SEUs (therefore low SEU rate) and do not have internal state (therefore will resume normal operation if the configuration is corrected), are not TMRed.

**Figure 44:** Majority voter circuit. On the Kintex Ultrascale firmware, the voter output is compared with every input to generate a "mismatch" output for monitoring purposes.

**Figure 45:** Block diagram of the Kintex Ultrascale firmware, with colors indicating the status of TMR protection. Green blocks are protected with TMR, yellow blocks are planned to be protected, and red blocks will not be protected.

The FPGA output signals can also be protected from radiation effects. The data-valid signals for the GBT protocol are output to the GBTx ASICs through triplicated pins, following the scheme shown in Figure 46.

Figure 46: Minority-voted outputs implement TMR on FPGA output pins. (From Xilinx XAPP197)

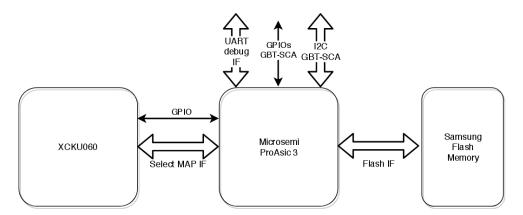

Second, the Kintex Ultrascale FPGA is continuously reprogrammed during operation: this "scrubbing" corrects configuration upsets before they can cause problems. As shown in Figure 47, this is done using two additional components: a radiation-hardened ProASIC3 FPGA that reprograms the Kintex Ultrascale FPGA, and a flash memory that holds the original "golden" firmware image. The Kintex Ultrascale FPGA supports programming and reprogramming through its SelectMAP interface. The ProASIC3 FPGA operates in two modes: initial programming, where the Kintex Ultrascale is reset, programmed from the golden image, and initialized; and scrubbing, where the Kintex Ultrascale is continuously reprogrammed without interrupting operation.

**Figure 47:** Block diagram of the RU scrubbing scheme, showing the XCKU060 Kintex Ultrascale FPGA to be scrubbed, the ProASIC3 FPGA that performs the scrubbing, and the flash memory that holds the golden firmware image.

Third, the ProASIC3 FPGA is protected from radiation effects. The configuration memory of the ProASIC3 FPGA is flash (as opposed to SRAM, as used in the Kintex Ultrascale) and is therefore immune to radiation effects. The combinatorial logic is also considered relatively insensitive. However, the flip-flops are still susceptible to SEUs, so TMR is still necessary. As shown in Figure 48, only firmware modules involved in the scrubbing functionality are protected with TMR. A simpler version of TMR, local TMR (see Figure 43), is used for the ProASIC3 FPGA: since the majority voter is combinatorial logic, it does not need to be triplicated. Also, since the configuration memory is SEU-immune, the ProASIC3 does not need to be

scrubbed.

Figure 48: Block diagram of the ProAsic3 firmware, with colors indicating the status of TMR protection.

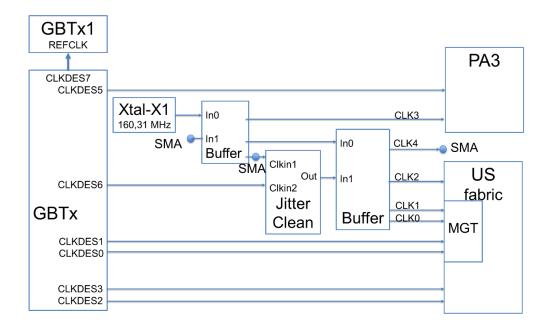

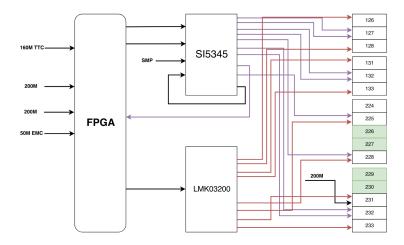

### 3.2.7 Clocking

Figure 49 gives an overview of the clocking scheme for the RU. The RU has two clock sources: a fixed-frequency crystal and the GBT clock from FELIX that is recovered by the GBTx ASIC. The GBT recovered clock can optionally be cleaned using a Si5338 jitter cleaner. A clock buffer IC on the RU selects between crystal and GBT clock inputs; the switch is controlled by the ProASIC3 FPGA, unless the component placement on the RU is modified to hard-wire the switch to select the GBT clock input (this was done for the 2018 beam test). The Si5338 is configured using toggle switches on the RU. The Kintex Ultrascale firmware can be compiled to choose between the clock buffer output and the raw GBT recovered clock for the user logic and for the GTH transceivers that receive ALPIDE data: the current MVTX firmware uses the clock buffer output for both.

# 3.2.8 Specifications

# 3.3 Interfaces

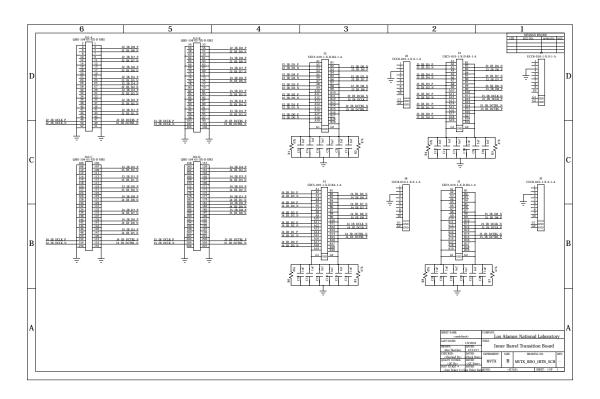

The RU connects to staves via Samtec FireFly cables. One RU connects to one stave through a transition board.

The stave has one clock line (unidirectional, RU-stave) and one control line (bidirectional) that are

Figure 49: Block diagram of the clock distribution on the RU.

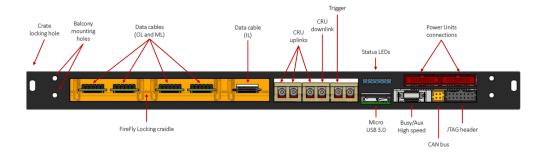

Figure 50: Front panel of the Readout Unit.

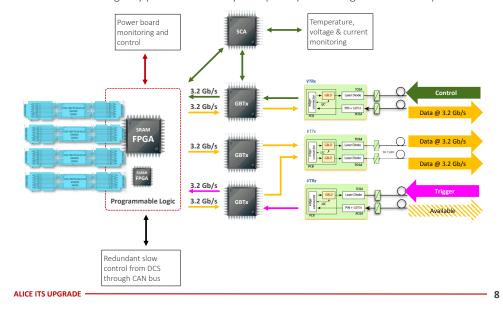

# Readout Unit – overall connections overview

- Direct connections to sensors control/clock and data lines.

- Fiber optic connection toward the CRU using the GBT chipset (3 GBTx + 1 SCA chip).

- CAN bus as emergency path to the DCS system (main path through CRU and GBT).

Figure 51: Block diagram of the Readout Unit's fiber links, including the mapping between GBTx chips and VTRx/VTTx fiber transceivers.

common to all ALPIDE chips, and nine data lines (unidirectional, stave $\rightarrow$ RU) that are connected to individual ALPIDE chips. Section 2.3 describes the ALPIDE interfaces.

Normally, all communication between the RU and the outside world — DAQ, slow controls, timing and trigger — takes place through the radiation-tolerant GBT (GigaBit Transceiver) fiber links. There is a backup path for slow controls through a CANbus interface. In addition, there is a port for a "busy" signal; this can be used to communicate the RU's busy status to a "Busy Unit" but could be used for another purpose.

As shown in Figure 51, the RU has three GBTx chips to support GBT fiber links. These support a total of two fiber inputs and three fiber outputs, which are driven/received by a combination of VTRx (transmitter+receiver pair) and VTTx (transmitter pair) modules. All optical interfaces use multimode fiber.

The GBTx, VTRx, VTTx, and GBT-SCA (Slow Controls Adapter) are all produced and supported by CERN as part of the Versatile Link project.

The RU receives trigger information from FELIX over a GBT link.

#### 3.3.1 GBT Interface

The current RU firmware only uses one GBT TX/RX pair. This pair uses a single VTRx module and the first GBTx on the RU ("GBTx 0").

The GBT link carries the following functions:

- Clock: the clock recovered from the RX link is used as the RU clock for FPGA logic and the GTH transceivers on the FPGA.

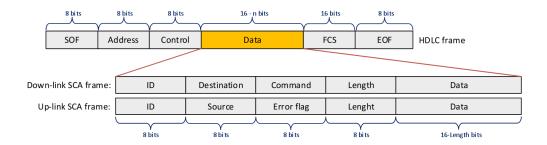

- GBTx control: the IC field of the RX GBT frame is interpreted by the GBTx ASIC and used for configuration and monitoring. This communication is based on the HDLC protocol. Responses are returned on the IC field of the TX GBT frame. The protocol is described in Figure 53.

- GBT-SCA control: the EC field of the RX GBT frame is transmitted to the GBT-SCA ASIC, which is used for slow controls on the RU (ADC, DAC, GPIO, JTAG). Responses are returned on the EC field of the TX GBT frame. The protocol is described in Figure 54.

- Trigger: the Kintex Ultrascale FPGA firmware recognizes special trigger words on the data-valid and data fields of the RX GBT frame. The format is described in Figure 52.

- Data: the Kintex Ultrascale FPGA transmits ALPIDE data using the data-valid and data fields of the TX GBT frame. The format is described in Figure 52.

## 3.3.2 I2C Interface to Power Boards

The Power Boards power the staves: they provide analog and digital supplies and bias voltage. Each Power Board is split into two Power Units. Each Power Unit can supply 8 analog, 8 digital, and 8 bias channels, and is controlled through two I2C buses (a "main" and a "aux" bus). One RU can control the four I2C buses on one Power Board: short ribbon cables connect the RU to the Power Board, and I2C blocks in the Kintex Ultrascale FPGA firmware interface the Wishbone bus to the Power Board.

### 3.3.3 RU interfaces to slow controls

The primary slow control interface is through the GBT links. The sPHENIX slow controls system will communicate with the RU through FELIX; the RU then controls the stave(s) and power board(s). A backup interface exists through the CANbus. Up to 20 RUs can share a single CANbus branch.

Remote reprogramming of the RU FPGAs will be supported: the GBT-SCA can act as a JTAG master that can be remotely controlled over the GBT link.

|          | DV |     | 79.                                  | .48    |        | _   | 43.        | .32    |      |       | 1     | 10    |

|----------|----|-----|--------------------------------------|--------|--------|-----|------------|--------|------|-------|-------|-------|

| TRIGGER  | 1  | ort |                                      | bit    |        |     | В          | С      |      |       | ty    | ype   |

|          | DV |     |                                      |        |        |     |            |        |      |       |       |       |

| IDLE     | 0  | 0   | 0:                                   | (000   | _000   | 00_ | _00        | 000    | _00  | 00_0  | 000   |       |

| SOP      | 0  | 1   | 1 0x000_0000_0000_0000               |        |        |     |            |        |      |       |       |       |

| HEADER 1 | 1  | 0>  | 0x00_0000 pri RUID 0xFFF             |        |        | FFF | FFF 0x0303 |        |      |       |       |       |

| HEADER 2 | 1  | 0х  | idno tidno_dd 0000x0                 |        |        |     | b it       |        |      |       |       |       |

| HEADER 3 | 1  | 0   | x0_00                                | 000_   | 0000   | 0   | typ        | pe     | 0 h  | bBC   | 0     | вс    |

| HEADER 4 | 1  | 0>  | 0x00_0000 over1 count 0x00_0000_0000 |        |        |     | 00         |        |      |       |       |       |

| DATA     | 1  | lan | e data                               | clata. | ciata. | da  | ia. c      | derte. | data | data. | data. | data. |

| DATA     | 1  | lan | e data                               | data.  | ciata. | da  | ta. c      | dada.  | data | data. | data. | data. |

| DATA     | 1  | lan | e data                               | data.  | data.  | da  | ia. c      | dada.  | data | data. | data. | data. |

| TRAILER  | 1  | Oxf | O seriosol Las                       | o      | tim    | eo  | uts        | 3      | o    | si    | lops  |       |

| EOP      | 0  | 2 ( | 2 0x000_0000_0000_0000_word.count    |        |        |     |            |        |      |       |       |       |

| IDLE     | 0  | 0   | 0:                                   | (000   | _000   | 00_ | _00        | 000    | _00  | 00_0  | 000   |       |

**Figure 52:** Trigger and data protocols for the data valid (DV) and data fields of the GBT frame. This corresponds to the RU firmware used at the 2018 test beam. Each DATA word contains a lane number and 9 ALPIDE data bytes from that lane. IDLE words may be inserted between DATA words.

Table 48 IC channel frame structure sent to GBTX for a write-read sequence

| Α | Frame delimiter 8'b 01111110                                  | Not in parity check |  |  |

|---|---------------------------------------------------------------|---------------------|--|--|

| В | GBTX i2c address (7 bits) + $R/W$ bit = 0 Not in parity check |                     |  |  |

| С | Command (8 bits) In parity check                              |                     |  |  |

| D | Number of data words n[7:0]                                   | In parity check     |  |  |

|   | Number of data words n[15:8]                                  | In parity check     |  |  |

| Е | Memory address [7:0]                                          | In parity check     |  |  |

|   | Memory address [15:8]                                         | In parity check     |  |  |

| F | 1st data (8 bits)                                             | In parity check     |  |  |

|   |                                                               | In parity check     |  |  |

|   | nth data (8 bits)                                             | In parity check     |  |  |

| G | Parity word (8 bits)                                          | In parity check     |  |  |

| Α | Frame delimiter 8'b 01111110                                  | Not in parity check |  |  |

Table 49 IC channel frame structure sent to GBTX in a read-only sequence

| Α | Frame delimiter 8'b 01111110              | Not in parity check |

|---|-------------------------------------------|---------------------|

| В | GBTX i2c address (7 bits) + $R/W$ bit = 1 | Not in parity check |

| С | Command (8 bits)                          | In parity check     |

| D | Number of data words n[7:0]               | In parity check     |

|   | Number of data words n[15:8]              | In parity check     |

| E | Memory address [7:0]                      | In parity check     |

|   | Memory address [15:8]                     | In parity check     |

| G | Parity word (8 bits)                      | In parity check     |

| Α | Frame delimiter 8'b 01111110              | Not in parity check |

Figure 53: The HDLC packet definitions for GBTx control over the IC link.

Figure 54: The HDLC packet definitions for GBT-SCA control over the EC link.

Figure 55: Block diagram of the functions of the GBT-SCA ASIC.

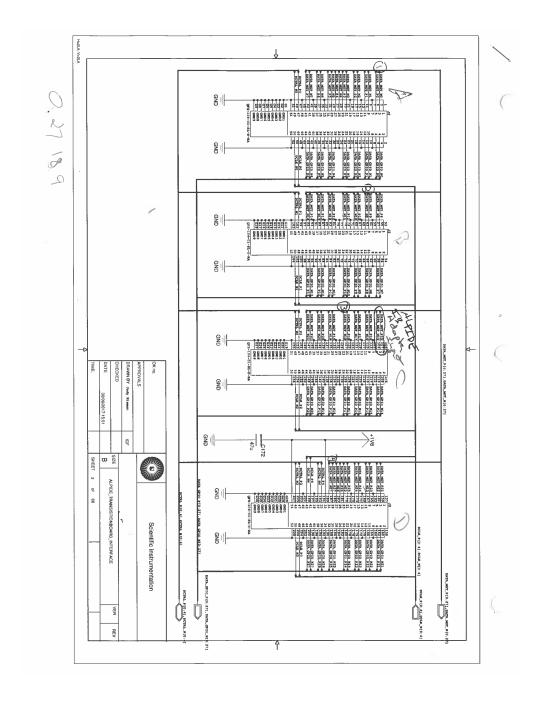

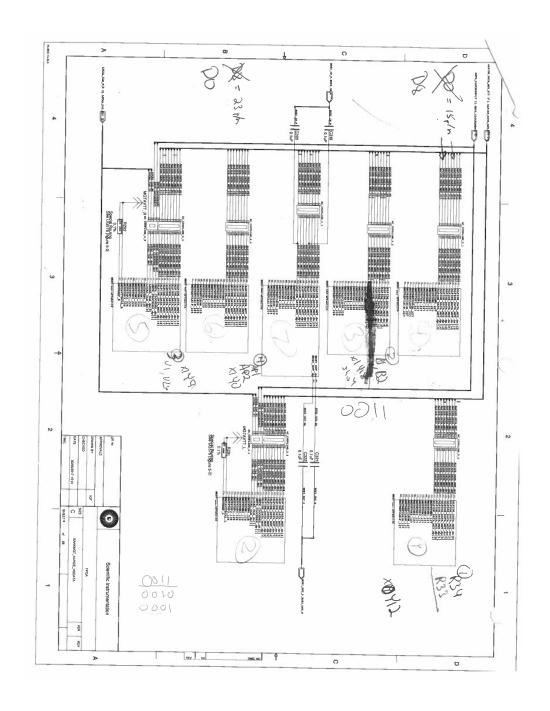

Figure 56: MVTX Readout Unit Inner Barrel Transition Board Schematic

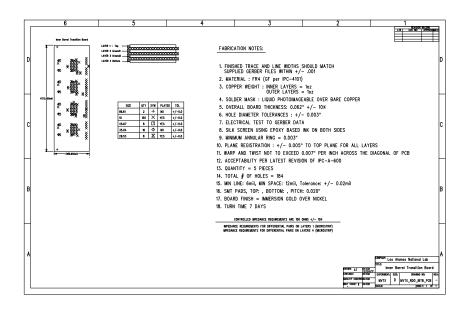

Figure 57: MVTX Readout Unit Inner Barrel Transition Board Fabrication Drawing

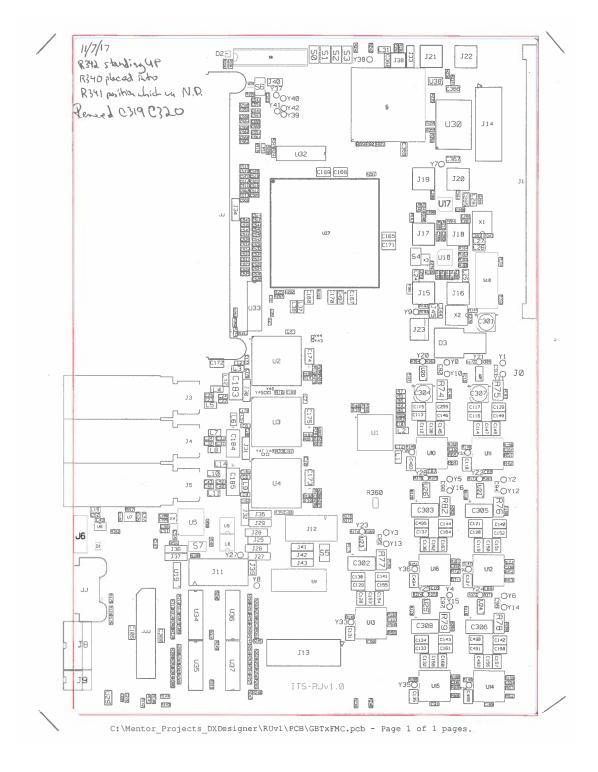

Figure 58: RDOv1 Modification Records

Figure 59: RDOv1 GT Mapping notes 1

Figure 60: RDOv1 GT Mapping notes 2

Figure 61: RDOv1 GT Mapping scratch pad

# 4 Back End Electronics

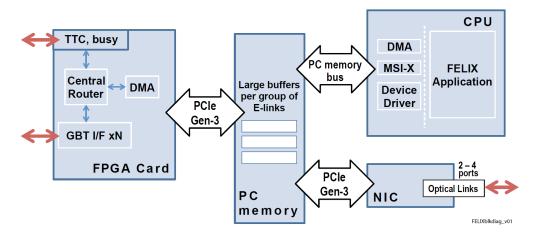

# 4.1 Description

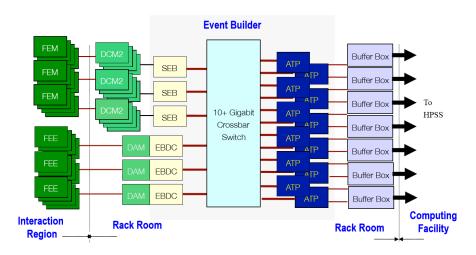

The sPhenix MVTX detector will use the Front-End Link eXchange (FELIX) system (developed for ATLAS upgrade) as a Data Aggregation, Data Formatting, and Data Acquisition infrastructure. The FELIX system will distribute Clock, Slow Control, and Trigger to the RU and ALPIDE.

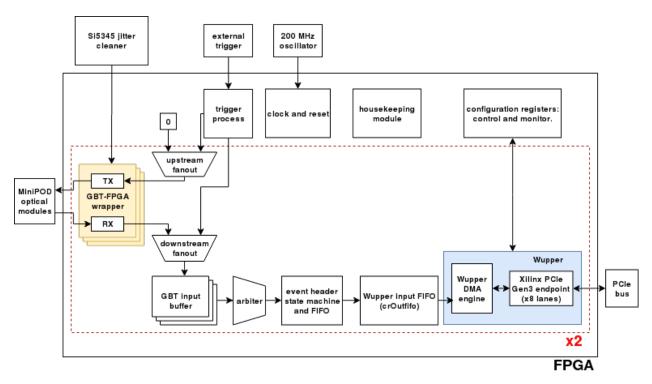

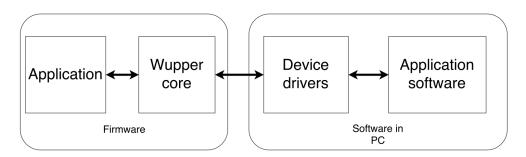

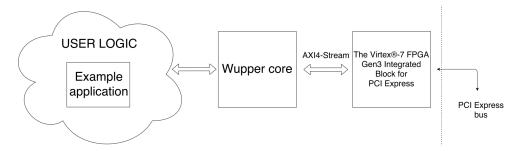

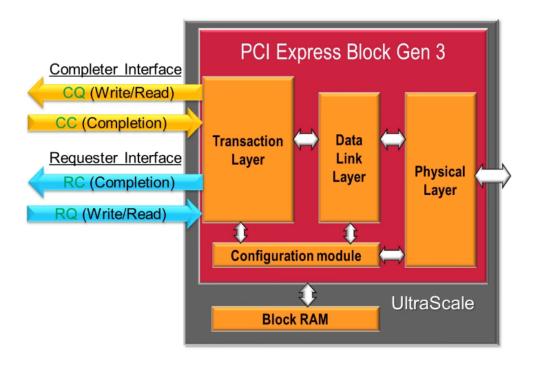

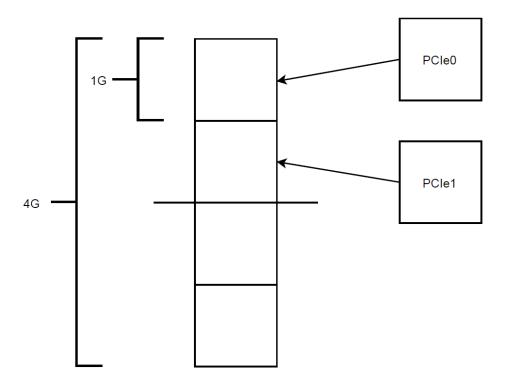

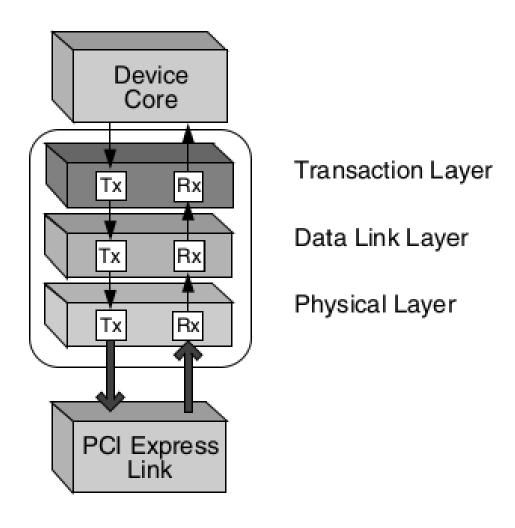

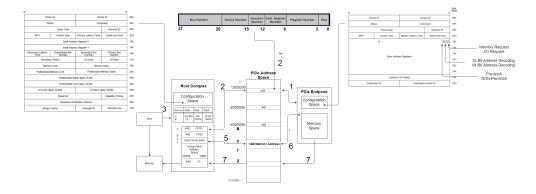

FELIX will serve as a PC-based gateway interfacing custom radiation tolerant optical links to PCIe Gen3. Figure 62

Figure 62: FELIX Block Diagram

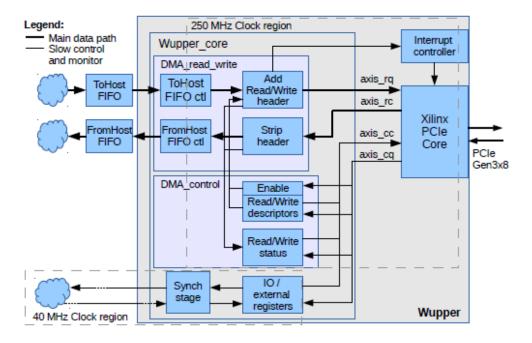

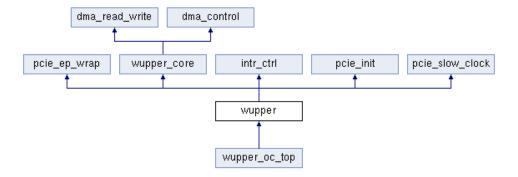

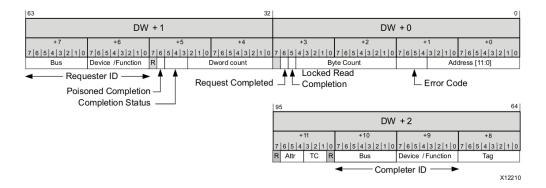

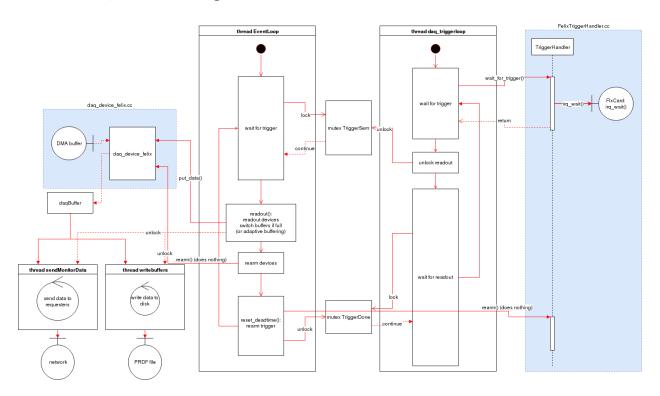

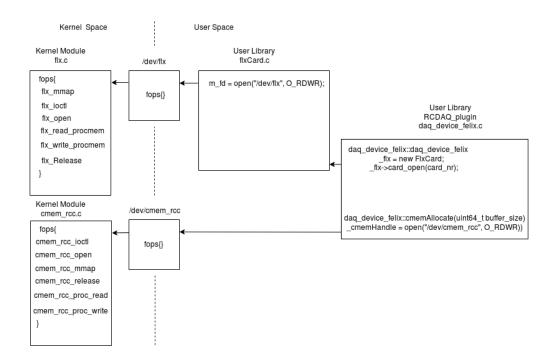

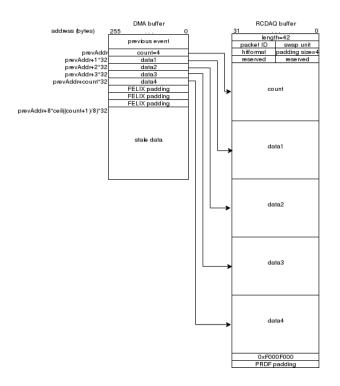

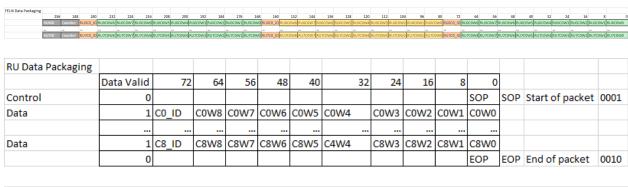

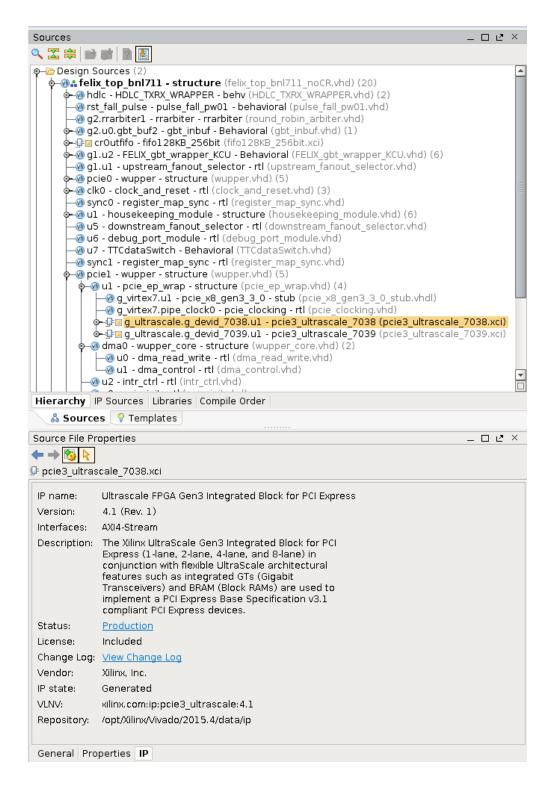

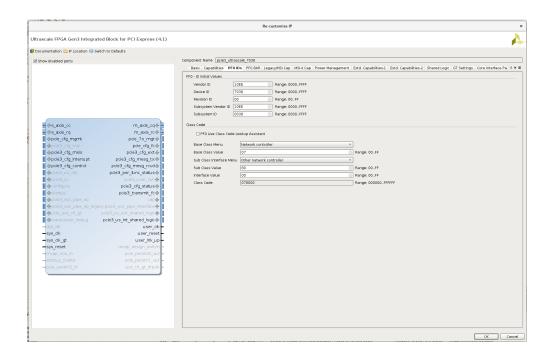

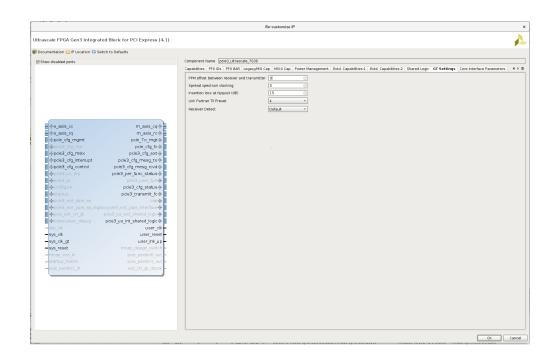

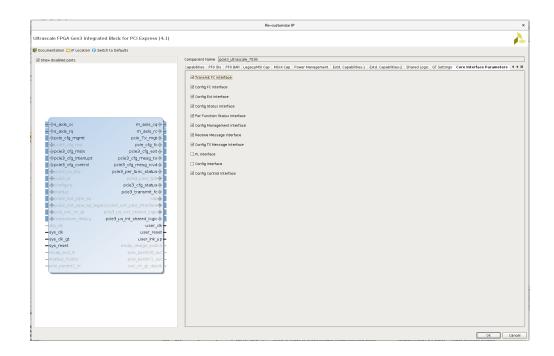

Figure 63 shows FELIX firmware architecture which primarily consists of 1) GBT-FPGA core, also referred to as "GBT wrapper," 2) the Central Router for internal data multiplexing, 3) the Timing and Trigger TTC decoder and 4) the DMA engine and PCIe engine referred to as "Wupper." The full list of top-level firmware modules is given in table 3.

The number of GBT links in the FELIX firmware, and other implementation-time options (listed in Table 4), are set in the implementation script do\_implementation\_BNL711.tcl. These options are set as generic parameters in the firmware. This allows the same firmware project to be used to generate bitstreams with different features, or for different hardware.

Figure 63: FELIX Firmware Diagram

### 4.2 GBT wrapper

The GBT wrapper is the bidirectional interface connecting the RU to FELIX via an optical link. The IP core was developed by CERN as part of the GBT-FPGA project and later enhanced by Kai Chen. The clocking methodologies will be described at a later time QPLL vs. CPLL. The difference between the GBT mode and full mode will also be explained at a later time. The MVTX detector will use GBT protocol.

Table 3: Top-level modules in the FELIX firmware.

| name                       | number of instances | description                                          |  |  |  |  |

|----------------------------|---------------------|------------------------------------------------------|--|--|--|--|

| upstream_fanout_selector   | 1                   | mux used to enable/disable sending triggers to FE-   |  |  |  |  |

| upstream_ranout_serector   | 1                   | LIX_gbt_wrapper_KCU inputs                           |  |  |  |  |

| EELIV abt wronner VCII     | 1                   | FPGA implementation of GBT protocol                  |  |  |  |  |

| FELIX_gbt_wrapper_KCU      |                     |                                                      |  |  |  |  |

| downstream_fanout_selector | 1                   | mux connecting the FELIX_gbt_wrapper_KCU out-        |  |  |  |  |

| 14 1 1 1 1 C               | CDT NUM             | puts and gbt_inbuf inputs                            |  |  |  |  |

| gbt_inbuf                  | GBT_NUM             | buffers and packs data words from GBT inputs         |  |  |  |  |

| rrarbiter                  | 1                   | arbitrates data transfer from gbt_inbuf buffers to   |  |  |  |  |

|                            | _                   | Wupper input FIFO                                    |  |  |  |  |

| wupper                     | 2                   | PCIe/DMA engine                                      |  |  |  |  |

| register_map_sync          | 2                   | clock domain crossing between PCIe clock and 40      |  |  |  |  |

|                            |                     | MHz clock                                            |  |  |  |  |

| clock_and_reset            | 1                   | instantiates MMCM clock managers, generates reset    |  |  |  |  |

|                            |                     | when clock is lost                                   |  |  |  |  |

| housekeeping_module        | 1                   | interface between register map and onboard devices   |  |  |  |  |

|                            |                     | (I2C, enable pins)                                   |  |  |  |  |

| pex_init                   | 1                   | initialize PEX8732 PCIe switch (I2C, hard-coded)     |  |  |  |  |

| not used for MVTX          |                     |                                                      |  |  |  |  |

| HDLC_TXRX_WRAPPER          | 1                   | interfaces GBT slow control links (IC/EC) to the FE- |  |  |  |  |

|                            |                     | LIX register map                                     |  |  |  |  |

| debug_port_module          | 1                   | output certain signals on test points                |  |  |  |  |

| ttc_wrapper                | 1                   | interface to ADN2814 CDR, decodes ATLAS TTC          |  |  |  |  |

|                            |                     | protocol                                             |  |  |  |  |

| TTCdataSwitch              | 1                   | switch between received TTC data and an emulator     |  |  |  |  |

| ttc_busy                   | 1                   | drives busy output                                   |  |  |  |  |

| LMK03200_wrapper           | 1                   | initialize LMK03200 jitter cleaner (SPI, hard-       |  |  |  |  |

|                            |                     | coded)                                               |  |  |  |  |

|                            |                     |                                                      |  |  |  |  |

Table 4: Options in the do\_implementation\_BNL711.tcl script.

| name                   | typical value | description                                        |

|------------------------|---------------|----------------------------------------------------|

| CARD_TYPE              | 711           | code indicating the board type (VC-709, HTG-710,   |

|                        |               | FLX-711), selects FPGA-specific (Virtex-7 vs. Kin- |

|                        |               | tex Ultrascale) behavior                           |

| GENERATE_GBT           | true          | generate the firmware blocks in the GBT data path  |

|                        |               | (rrarbiter, gbt_inbuf, FELIX_gbt_wrapper_KCU,      |

|                        |               | upstream_fanout_selector)                          |

| DEBUG_MODE             | false         | in debug_port_module.vhd, enable debug output to   |

|                        |               | test points                                        |

| GBT_NUM                | 6             | number of GBT links                                |

| PLL_SEL                | CPLL          | PLL (CPLL or QPLL) type for the GTH transceivers   |

|                        |               | used for GBT                                       |

| USE_BACKUP_CLK         | true          | use onboard fixed oscillator (vs. TTC clock)       |

| AUTOMATIC_CLOCK_SWITCH | false         | automatic switching between onboard and TTC        |

|                        |               | clocks                                             |

| NUMBER_OF_INTERRUPTS   | 8             | number of interrupts per Wupper PCIe/DMA engine    |

| NUMBER_OF_DESCRIPTORS  | 2             | number of descriptors per Wupper PCIe/DMA en-      |

|                        |               | gine                                               |

| PCIE_PLACEMENT         | SLR0          | which side of the FPGA to place the second PCIe    |

|                        |               | endpoint (differs between FELIX v1.5 and v2.0)     |

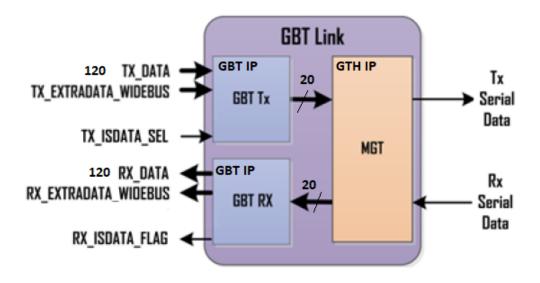

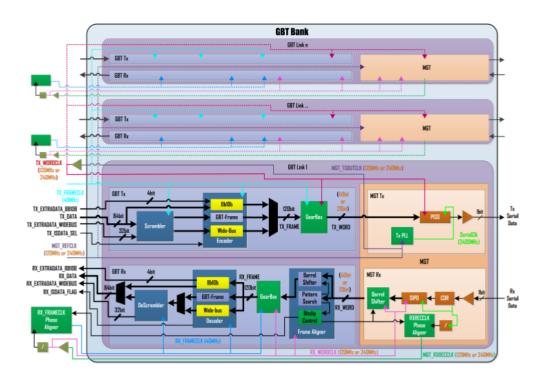

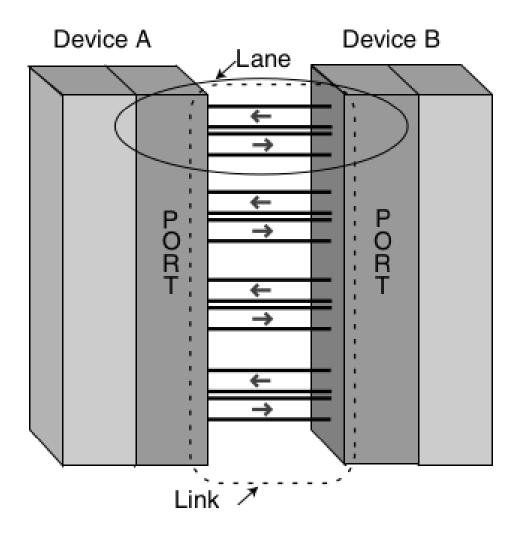

The wrapper integrates several GBT links. Figure 64 shows a block diagram of a single GBT link or the actual channel. It is composed of a GBT and GTH IP. The GBT IP consists of GBT Tx (that scrambles and encodes the transmitted parallel data), and GBT Rx (that aligns, decodes and descrambles the incoming data stream) which implement the GBT protocol. The GTH IP consists of the Multi-Gigabit Transceiver (MGT) (that serializes, transmits, receives and de-serializes the data). The MGT is the dedicated Serializer/Deserializer (SerDes) in the FPGA . CPLL and QPLL are inside the MGT. Figure 65 shows a detailed block diagram of the GBT and GTH IP. The following section describes each block and the GBT frame shown in figure 97

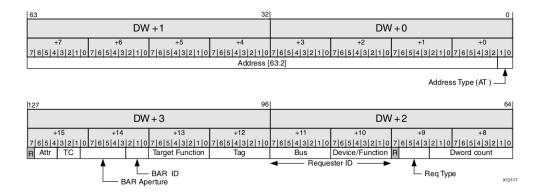

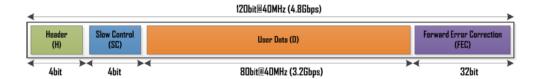

DC-balance of the data being transmitted over the optical fiber is ensured by scrambling the data. For forward error correction the scrambled data and the header are Reed-Solomon encoded before serialization. The 84-bits (80 bits data, 2 bits IC and 2 bits EC) are first processed by the scrambler, the header is then added (4 bits), the Reed-Solomon (RS) encoding and interleaving takes place and finally the data is serialized. While the scrambler maintains the word size, the RS encoder adds the 32-bit Forward Error Correction (FEC) field adding up to a total frame length of 120 bits. This leads to an overall line code efficiency of 84/120 = 70 percent. At the receiver end the inverse operations are repeated in the reverse order. The fact that RS encoding and decoding are the first and the last operations to be done respectively at the transmitter and receiver (before transmission and after reception) ensures that transmission errors do not get multiplied by the scrambler operation.

### 4.3 Data Processing

Figure 64: GBT Wrapper

Figure 65: GBT TX RX Block Diagram

Figure 66: FELIX MVTX Datapath

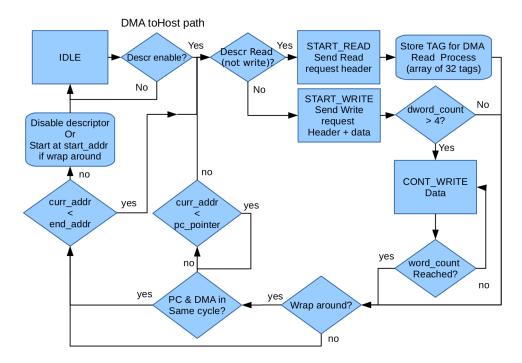

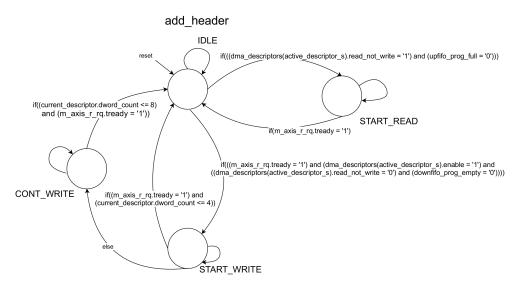

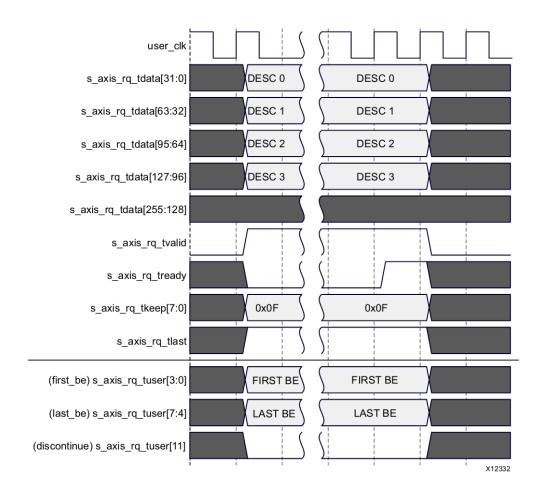

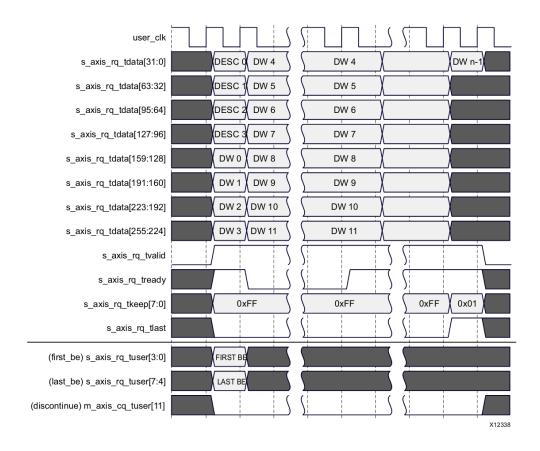

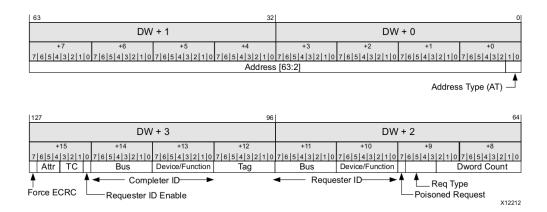

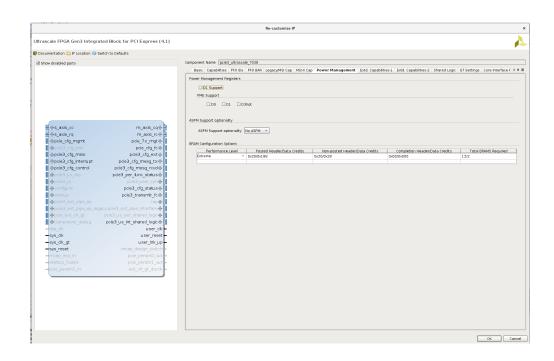

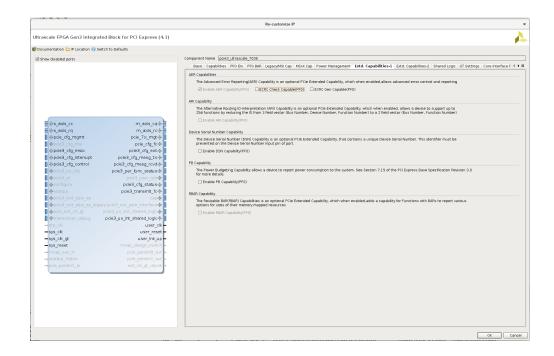

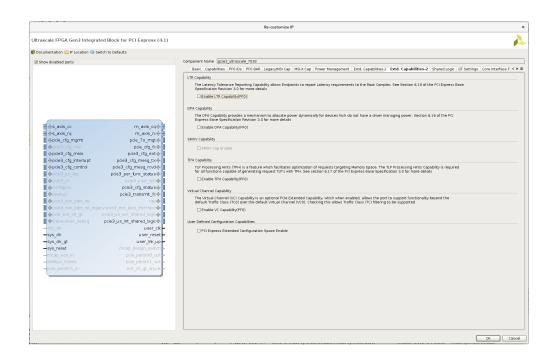

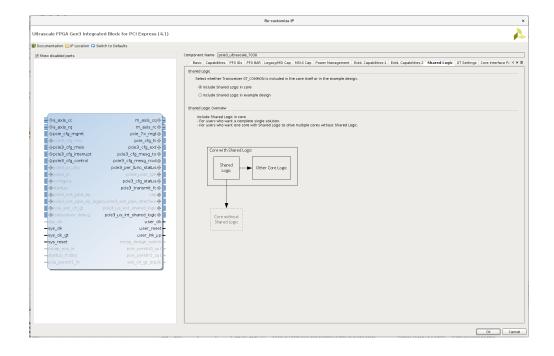

# 4.4 Wupper