# DAQ for FVTX detector Implementation

Mark Prokop

Los Alamos National Laboratory

#### Talk Outline

- Overall Readout System

- ROC Pre-Production Prototype

- FEM Pre-Production Prototype

- Risk Factors

- Summary

#### Technical Challenges for Readout

- Challenges

- Radiation environment around the detector

- 10 year Total Integrated Dose - <200 kRad</li>

- Acute Radiation Effects on FPGA configuration SRAM memory

- Data Bandwidth

- 3.38 Terabits/sec

- Number of Data I/O Lines

- ~17k LVDS Pairs

- Solutions

- Use Radiation Tolerant FPGAs close to the detector

- ACTEL FLASH based FPGA

- IR Data Compression Circuitry

- Sync word removal

- FO Data Transport to FEM

- 16 2.5 Gigabit/sec FO data links

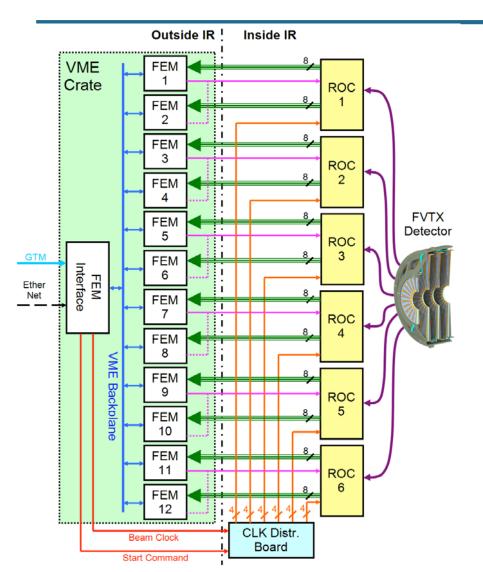

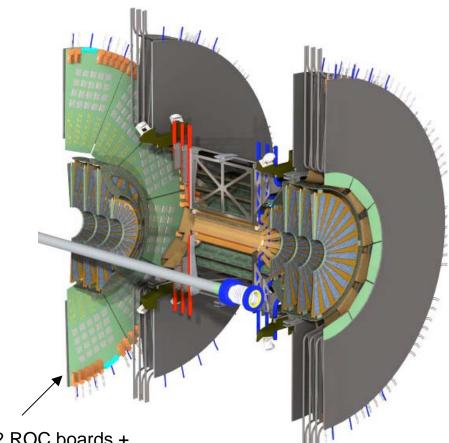

# Overall Readout Strategy

- ½ of each detector arm is read out independently

- 6 ROC cards collect and compress the data from the detector

- Each ROC card sends fiber output to two FEM boards in the Counting House

- Slow Control fiber sends control data stream up/down the FEM↔ROC Slow Controls link

- Clock Distribution Board distributes Beam Clock and Start signals to individual ROC boards (the signals are sent over dedicated optical fibers)

### DAQ

- ROC board layout started

- Clock Distribution Board layout started

- Components, cost, power consumption estimated

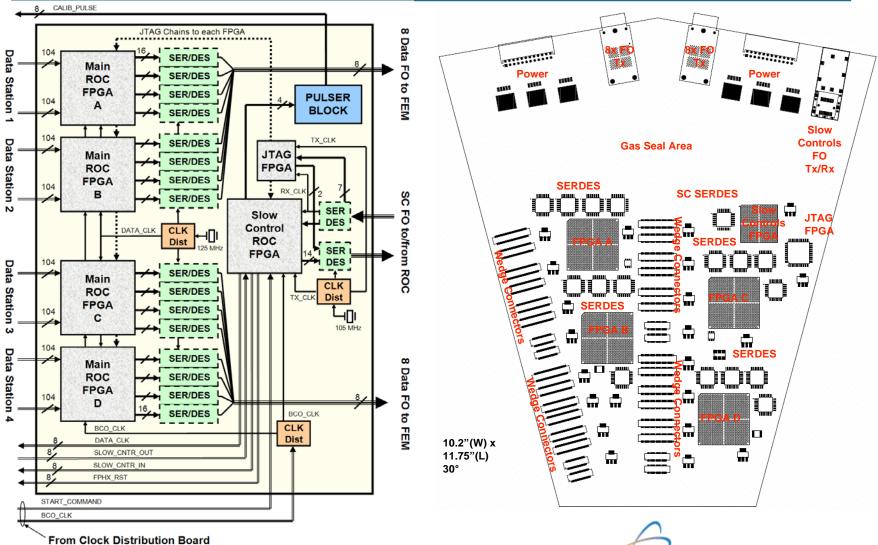

- Electronics supply voltages regulated on ROC

- Voltages Required:

- 3.3V: FO Tx/Rx

- 2.5V: SERDES, ROC I/O, Wedge

- 1.5V: FPGA Core

- Total power per ROC board

- ~ 20 W board + 18 W for V regulators

- = 38 W

- Total Power per ½ Arm = 228 W

- Total Power per Arm = 456 W

- Total Power for Detector = 912 W

12 ROC boards +

2 Clock Distribution

boards in a "big

wheel"

# ROC Board - WBS 1.5.2

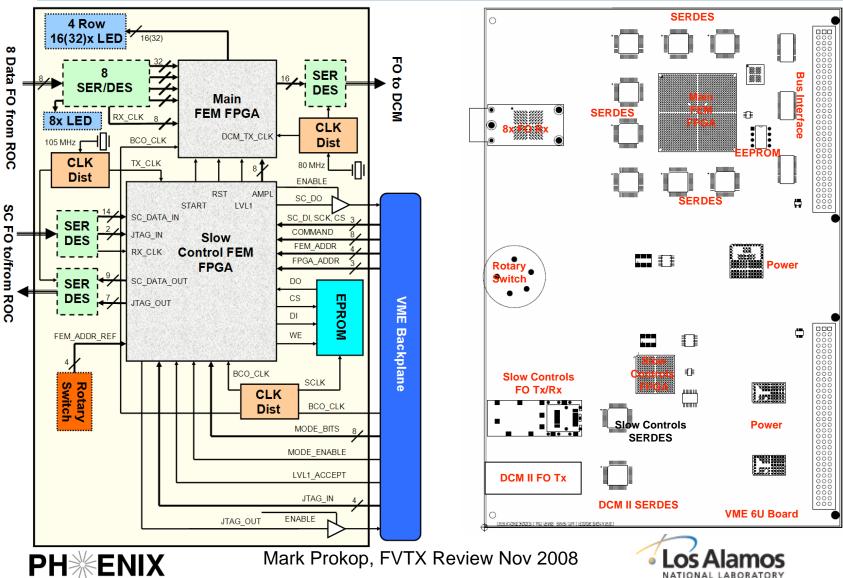

## FEM Board – WBS 1.5.3

### Risk Factors

- FVTX DAQ design utilizes well tested, commercially available parts, nothing "state-of-the-art".

- Risk low

- Design of the ROC requires a significant amount of digital signal tracing and excellent ECAD skills.

Risk – moderate

- FEM board is simple VME board with a few components. Moderate number of I/Os.

Risk – low

None of the WBS 1.5 items is on the critical path

#### Summary WBS 1.5 – Technical

Specification Document

Prototype status

Electronics Components

Production Quantities

Heat load

On-project Manpower

Institutions Involved

Infrastructure Defined

QA procedures in place

TDR, DAQ overview document

ROC and FEM pre-production

prototypes - started

All available from distributor stock

24 + 4(spares) ROC boards

48 + 6(spares) FEM boards

38 W per ROC board

456 W per arm

1 EE + 1 ECAD

LANL

draft

Full QA plans for ROC and FEM

# DAQ Implementation

### Backup Slides

#### Summary WBS 1.5 - Schedule

PHENIX System Test: 1/09-3/09

ROC Pre-prod Proto: 10/08-1/09

FEM Pre-Prod Proto: 3/09-7/09

• ROC Production: 10/09-1/10

• FEM Production: 10/09-1/10

#### Summary WBS 1.5 - Cost

ROC Pre-production: \$74k

FEM Pre-production: \$85k

• ROC Production: \$390k

• FEM Production: \$350k

Ancillary: \$116k

Fibers and Lab Equipment: \$124k