# DAQ & Electronics for the CW Beam at Jefferson Lab

**Benjamin Raydo**

EIC Collaboration @ Stony Brook January 10-12, 2010

# Goals for EIC Trigger

#### **High Event and Data Rates**

- Trigger must be able to handle high luminosities (and hadron multiplicities)

- 10<sup>32</sup>-10<sup>33</sup> for eRHIC and 10<sup>34</sup>-10<sup>35</sup> for EIC@JLab (ELIC)

- Trigger rate depends on e-p interaction rate ( $\mathcal{L}\sigma$ ), not bunch crossing frequency

- events will be read out when trigger occurs

- as in CLAS, the time reference is provided by tracking the electron (stable  $\beta=1$  particle)

#### **Other Requirements**

- High efficiency for rare triggers and low electron energies

- Minimum-bias trigger with limited (if any) prescale for low-Q<sup>2</sup> events

- Random background suppression at L1 trigger (track vertex reconstruction, etc)

#### **Rate estimates**

- H1/ZEUS at 5 x 1031: < 1000 Hz @ level-1, 10 Hz @ level-3 to tape

- CLAS12 at  $10^{35}$ : 10 kHz @ level-1 to tape (mostly  $\pi$  due to low Cerenkov thresholds)

- EIC at a few x 10<sup>34</sup> (estimated): ~100 kHz @ level-1

#### Implementation can be based on JLab 12 GeV trigger experience

- High-rate capability (200 kHz) from GlueX hadron trigger

- Advanced algorithms from CLAS12 trigger

# **CW Trigger Talk Overview**

- 1. JLab CW Accelerator Facility

- 2. Pipelined Trigger Overview

- 3. Pipelined front-ends: Flash ADC

- 4. Forming Triggers

- 5. Some Trigger Implementations at JLab

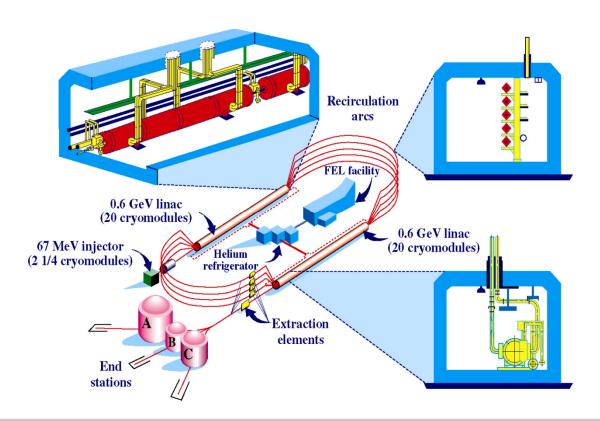

### 1.0 JLab CW Accelerator Background

#### **CEBAF**

- Two recirculating Linacs operating at 1497MHz

- Three beams produced at the injector with 120 degrees of phase separation

- Beams delivered to three experimental halls at 499MHz

- Continuous Wave (CW) bunches at ~2ns on fixed targets → →

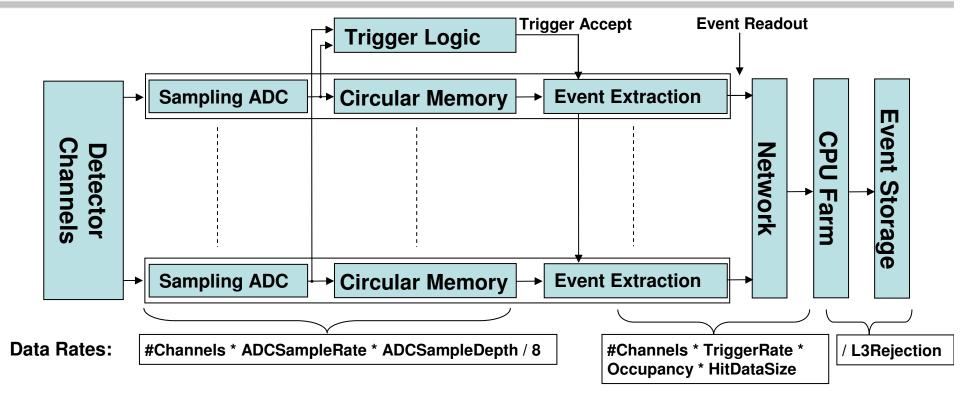

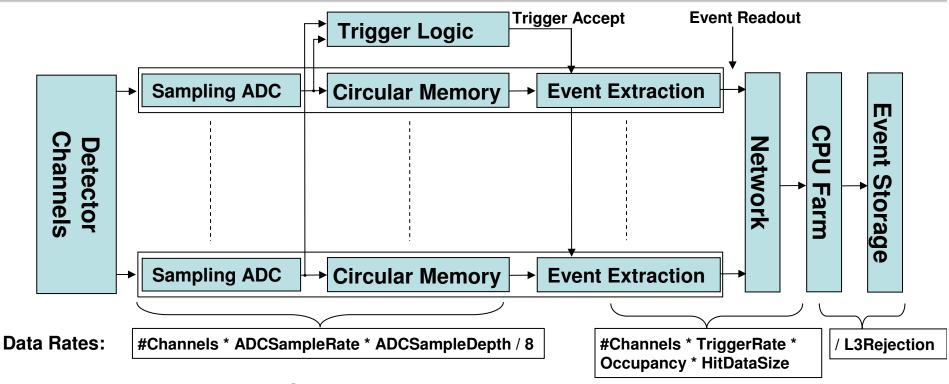

# 2.0 Pipelined DAQ & Trigger Architecture

- All channels are continuously sampled and stored in a short term circular memory

- Channels participating in trigger send samples to trigger logic. When trigger condition is satisfied, a small region of memory is copied from the circular memory and processed to extract critical pulse details such as timing & energy. **This** essentially makes the event size independent of ADC sampling rate, depth, and number of processed points.

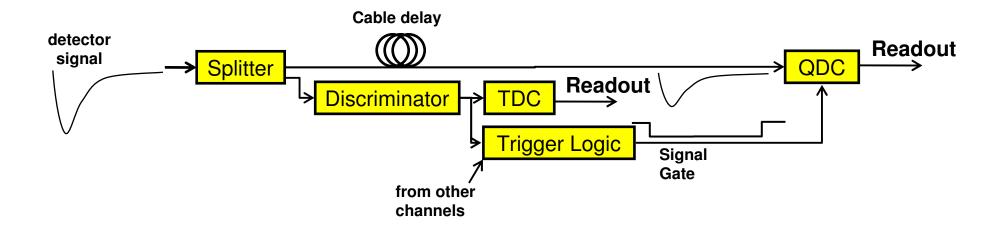

# 3.0 Traditional Method of Signal Capture

- Requires multiple modules to acquire time and/or charge

- Detector signals must be delayed to allow trigger decision time to form gate

- Very limited trigger logic resolution or very complex/expensive to build

- Gated readout modules typically have large conversion times, creating dead-time

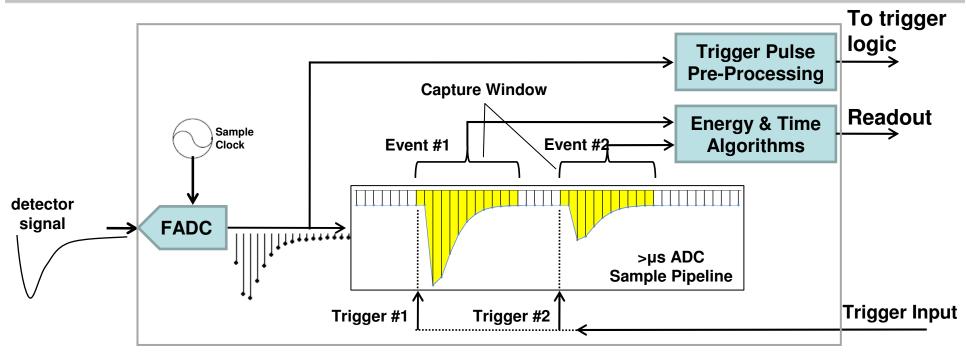

### 3.1 Modern Method of Signal Capture

- Sampling Flash ADC stores digitized signal in large memory with trigger decision made

- Trigger input copies a window of the pipeline and extract pulse charge and time for readout

- •Trigger output path contains detailed information useful for cluster finding, energy sum, etc.

- Hardware algorithms provide a huge data reduction by reporting only time & energy estimates for readout instead of raw samples

# 3.2 Pipelined DAQ & Trigger Architecture

For example, the Hall D GlueX Experiment we can calculate the following:

125Msps 12bit ADC: ~13,000 channels => 13,000 \* 125,000,000 \* 12 / 8 = 2.4375 TB/sec

250Msps 12bit ADC: ~6,000 channels => 6,000 \* 250,000,000 \* 12 / 8 = 2.25 TB/sec

A total of ~5 TB/sec directly from detector. However:

Expected trigger rate is <200kHz, Occupancy ~6%, HitChannelEventSize ~18bytes, L3Rejection ~10

Readout total of ~3GBytes/sec. Farm rejection factor 10 => ~300MBytes/sec to disk.

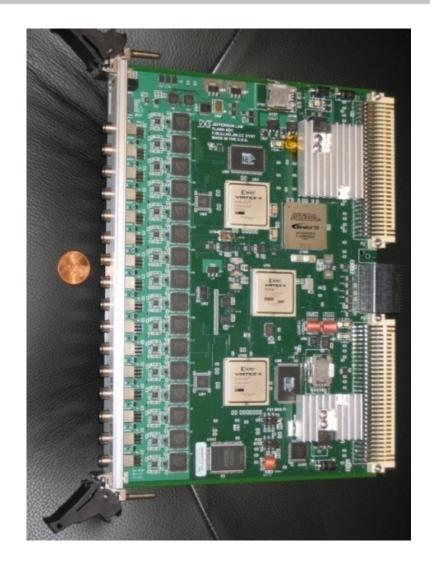

# 3.3 Example: JLab Pipelined Flash ADC

- 16 Channel 12bit, 250Msps Flash ADC

- 8μs raw sample pipeline, >300kHz sustained trigger rate (bursts @ ~15MHz)

- Post-processing in customizable firmware to extract time, charge, and other parameters minimizing event size

- Module supports 2eSST VME transfers at 200MB/s transfer rate

- Large event block sizes (>100) to minimize CPU interrupt handling

- VXS P0/J0 outputs 5Gbps L1 data stream (hit patterns, energy sum, pulses)

- Used in existing 6GeV program:

Hall A BigBite & Moller Polarimeter

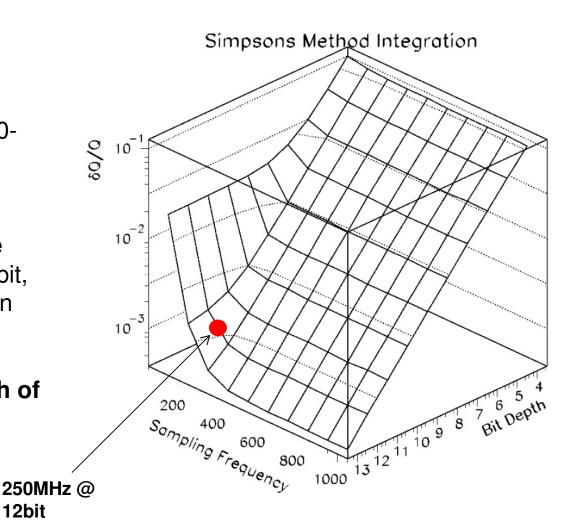

# 3.4 FADC Sampling – Charge Accuracy

#### Hall D FCAL PMT: FEU 84-3

- -10,000 Random height pulses 10-90% full scale of ADC range simulated

- Sampling frequency makes little difference beyond 250MHz at 12bit, providing ~0.1% charge resolution

- PMT pulse shape dominates sample frequency and bit depth of ADC

From: GlueX Doc# 425-v1

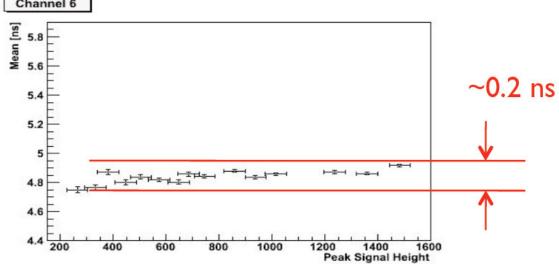

# 3.5 FADC Sampling – Timing Accuracy

#### Hall D FCAL PMT: FEU 84-3

- Timing algorithm developed & tested by Indiana University for the Hall D forward calorimeter.

- Implemented on the JLab FADC250 hardware achieving <300ps timing resolution on 50% pulse crossing time with varied signal heights.

- Resolution allow reliable information to link calorimeter with tagged electron bunch.

Typical timing resolution achieved ~1/10 the sample rate. The PMT shape will drive the ADC sample rate & depth requirements.

From: GlueX Doc# 1258-v1

### 4.0 Forming Triggers

#### Rate = $\mathcal{L} \times \sigma \sim 100$ kHz for EIC

- Bunch crossing rate of 1.5GHz and Interaction rate of ~100khz we get an **e-p interaction of interest every** ~10<sup>4</sup> bunch crossings

- A trigger occurs when trigger condition is satisfied, which is computed asynchronously with bunch crossing

- As in CLAS, the time reference is provided by tracking the electron (stable  $\beta$ =1 particle)

#### **Hardware Triggering Options**

Background suppression achieved by using advanced trigger algorithms:

- Calorimeter cluster finding (sliding window, cluster size & energy)

- Track reconstruction (Shift/sum methods, Hough transform, vertex finding)

- Geometrical matching between detectors

JLab is experienced and planning these types of trigger designs for existing experiments (6GeV and 12GeV trigger designs)

# 5.0 JLab Trigger Designs

### **Existing 6GeV CLAS Trigger**

- 5.1 CLAS detector overview

- 5.2 CLAS global trigger design

- 5.3 Inner Calorimeter cluster finding

### **12GeV Pipelined Trigger Designs**

- 5.4 12GeV Pipelined Trigger

- 5.5 GlueX Trigger

- 5.6 CLAS12 Trigger

- 5.7 CLAS12 Cluster Finding

- 5.8 Prototyped System

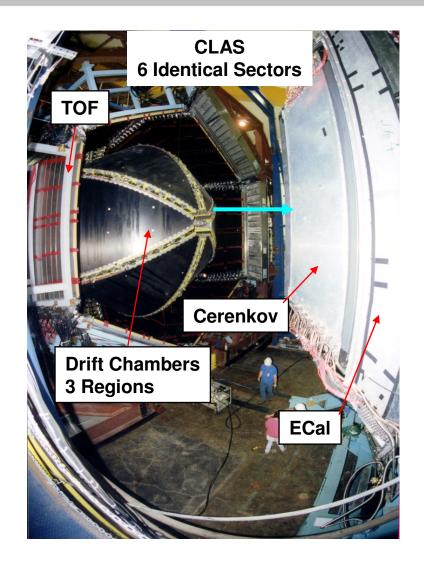

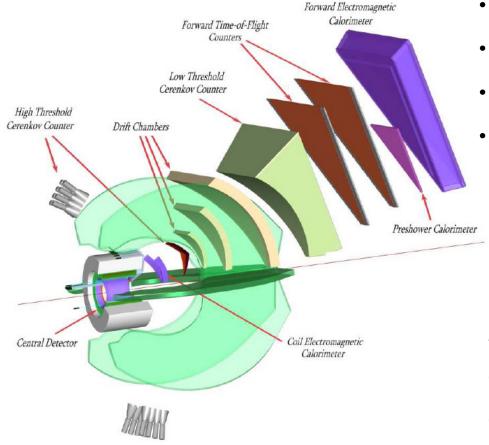

# 5.1 Existing CLAS Detector & Trigger

- Photon & Electron Experiments with polarized targets, polarized beam

- High Luminosities a few x10<sup>34</sup>cm<sup>-2</sup>s<sup>-1</sup>:

- DAQ L1 event rate designed to ~10KHz

- FPGA based Level 1 Hardware

- Pipeline design, Dead-timeless, (5ns pipeline clock)

- Low latency (~150ns)

- Fast Level 1 for ADC Gate, TDC Start

- TOF, Cerenkov, Electromagnetic Calorimeter

- Pattern recognition programming

- Sector based logic for L1 trigger 'equations'

- · Cluster finding for Inner Calorimeter

- •Up to 32 Front End ROCs

- Fastbus, VME, [TDC; ADC; Scalers]

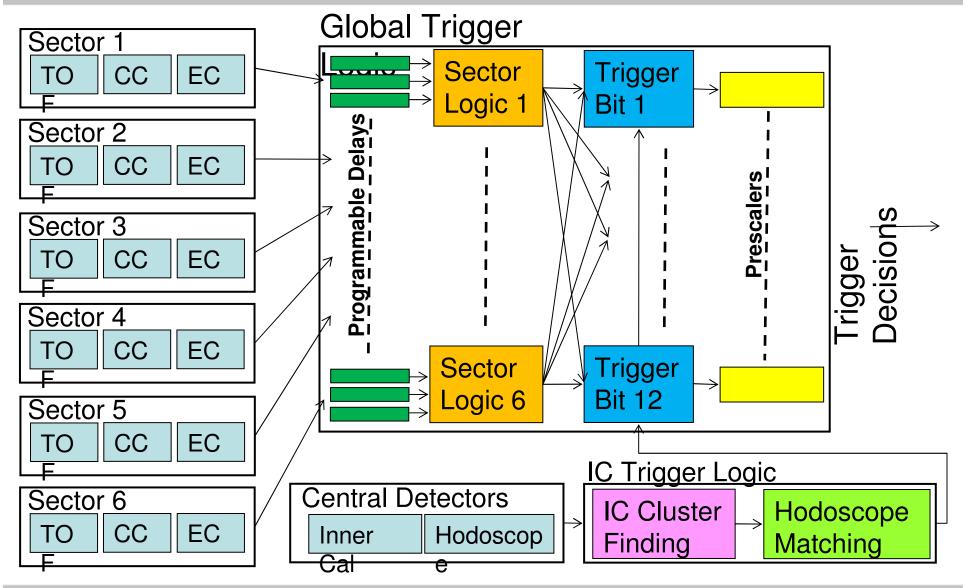

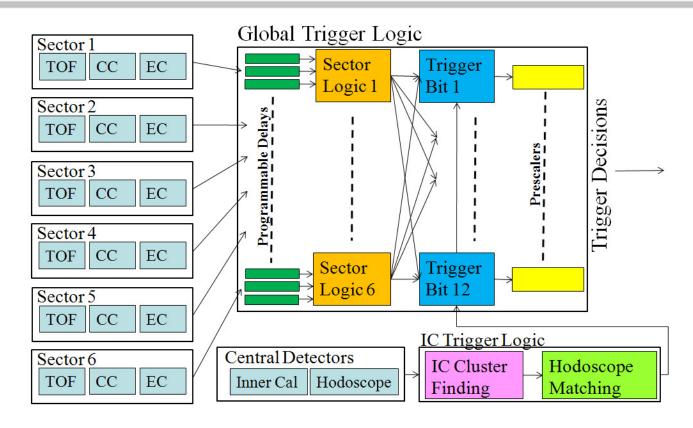

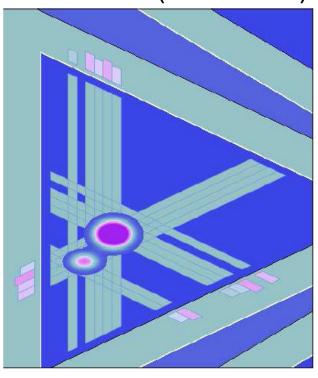

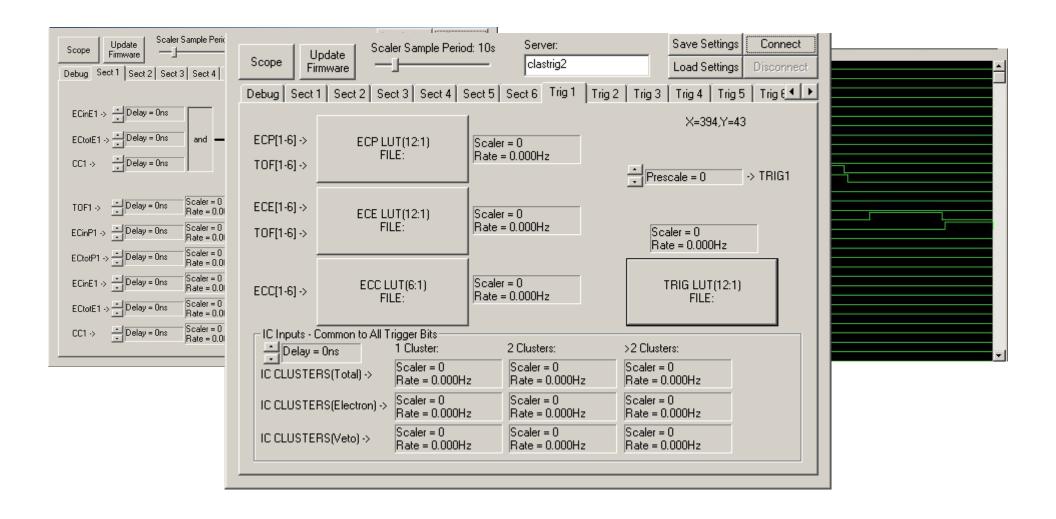

# 5.2 Existing CLAS Trigger

- Fast L1 trigger design for CLAS

- Sector based triggers combined with central detector information

- Very fast cluster finding trigger for Inner Calorimeter (IC)

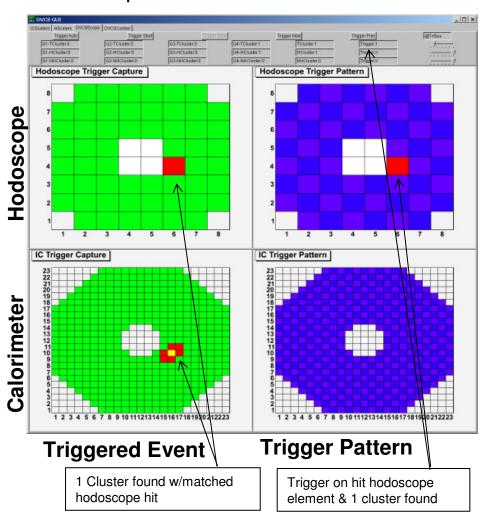

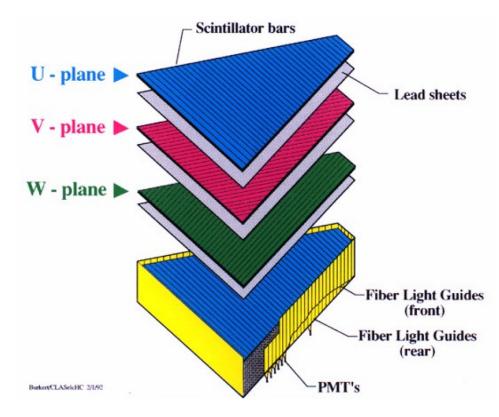

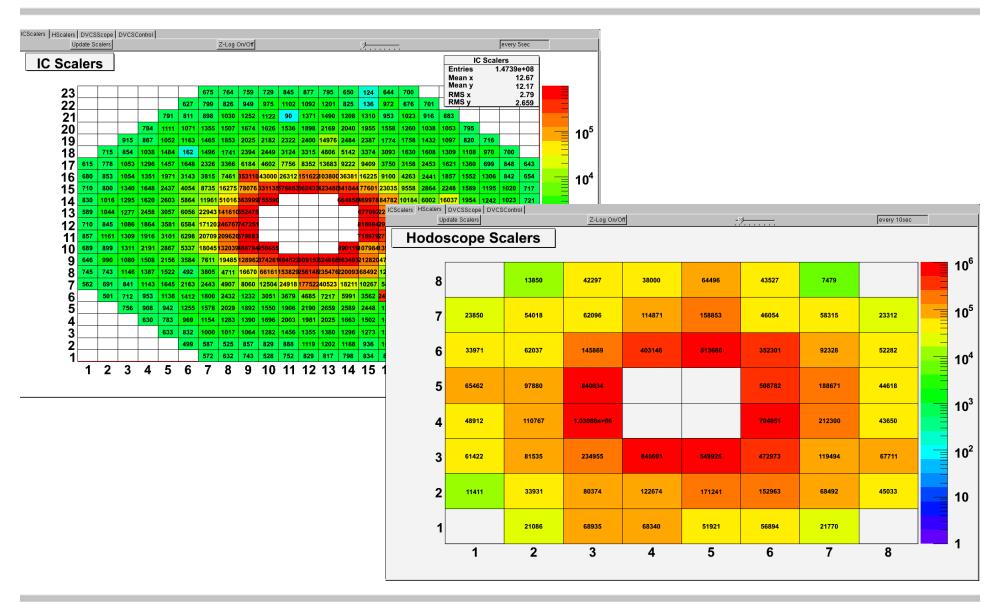

# 5.3 IC Cluster Finding Trigger

424 Tower PbWO<sub>4</sub> Calorimeter & 56 Channel Hodoscope

- FPGA based trigger finds all clusters with calorimeter by considering all possible views with a 3x3 "sliding" window

- Cluster decisions can optionally be geometrically matched with hodoscope

- Decision time ~85ns, 66MHz pipeline

- Trigger module has a parallel diagnostic trigger that allows arbitrary triggers to be setup for algorithm/channel/timing verification (does not interfere with data taking)

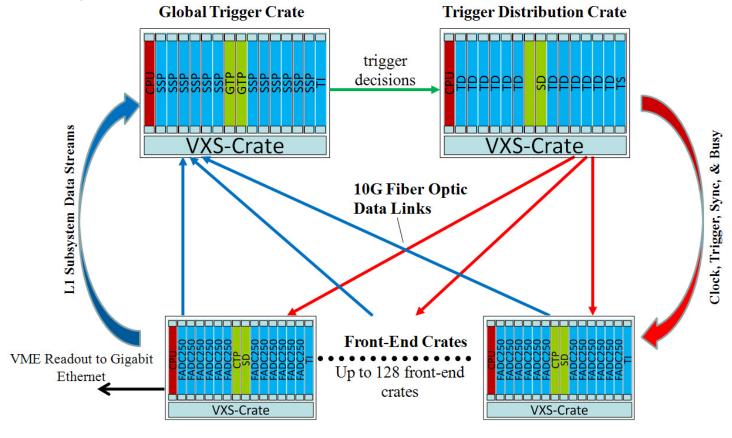

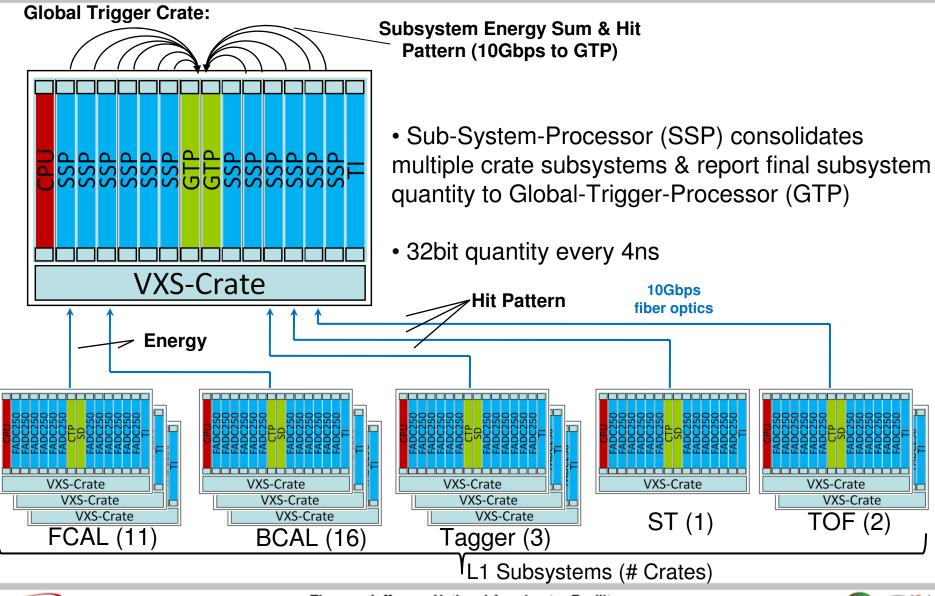

### 5.4 12GeV JLab Pipelined Trigger Design

- Designed for experiments at CLAS12 & GlueX

- 125/250MHz Flash ADC based front-ends

- >300kHz Trigger rate capable

- High speed L1 trigger system (heavily based on high speed serial links & large FPGA processing)

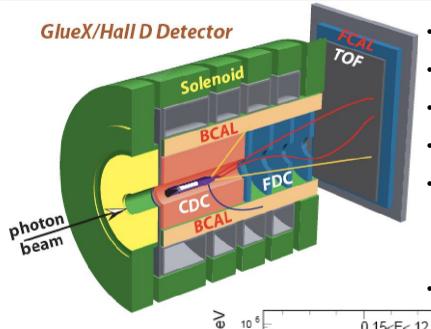

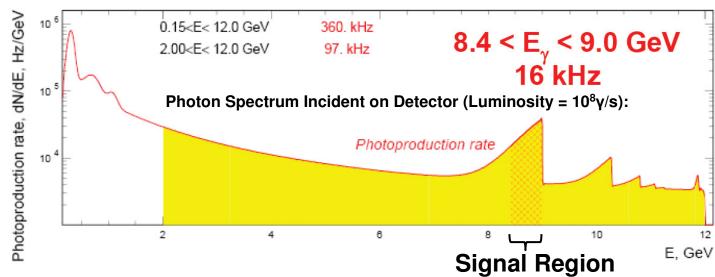

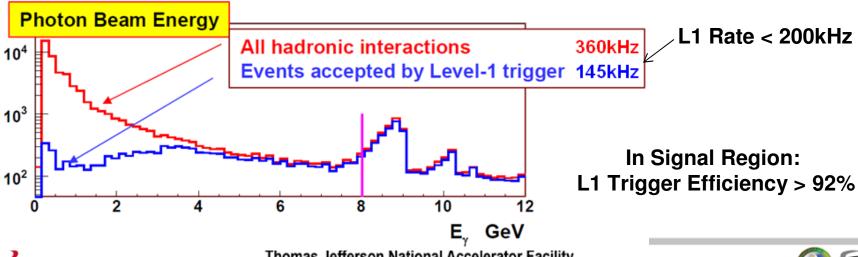

### 5.5 Hall D – GlueX Detector

Photon beam experiment

Channel count: ~22,000

Luminosity: 108y/s

L1 Acceptance: <200kHz</li>

Main L1 Trigger Algorithms:

Energy sums

Hit multiplicities

Low energy pulse suppression

Suppress 360kHz hadronic & 200MHz EM Background

# 5.6 CLAS12 Trigger Design

Channel count: ~40,000

• Luminosity:  $\sim 10^{34} \text{cm}^{-2} \text{s}^{-1}$

• L1 Acceptance: <20kHz

Main Trigger Algorithms:

EC Cluster Finding

DC Road Finding

Geometric Matching Clusters & Tracks

#### **Advanced trigger supports:**

- -Reliable electron identification

- -Multi-particle events

# 5.7 Ex: Forward Calorimeter Cluster Finding

# Calorimeter cluster reconstruction (1 sector shown):

#### **Calorimeter construction:**

- Cluster reconstruction will be formed in L1 trigger level and matched with drift chamber tracks for each sector.

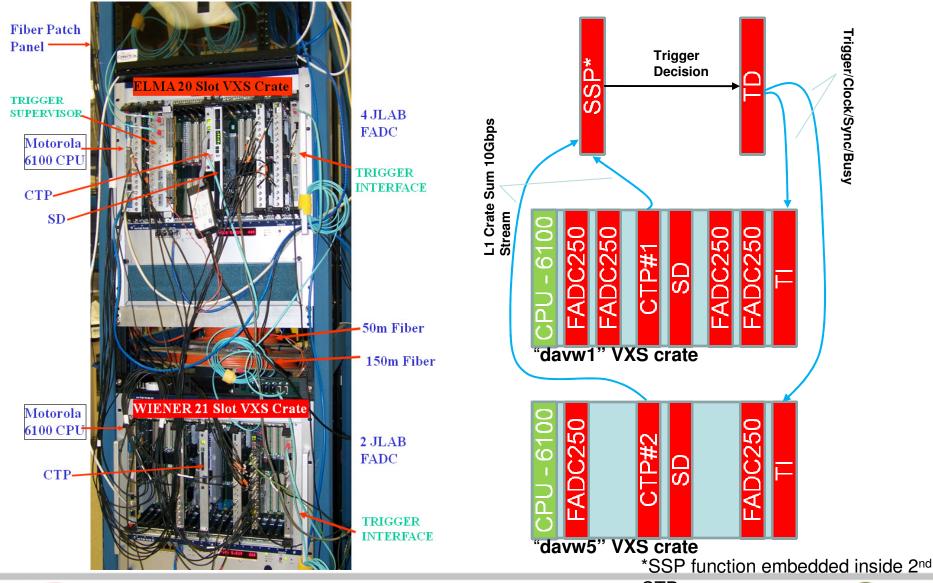

### **5.8 2 Fully Prototyped Front-End Crates**

### In Conclusion...

- EIC Triggering will need modern trigger system & DAQ to support high trigger rates and suppress background events

- JLab 6GeV experience and 12GeV developments address many of the issues surrounding high speed trigger development & advanced trigger support

- At JLab we've had no problem with 500MHz bunch crossing beam for existing experiments and see no reason why 1.5GHz will be different since the trigger rate does not depend on the bunch crossing rate

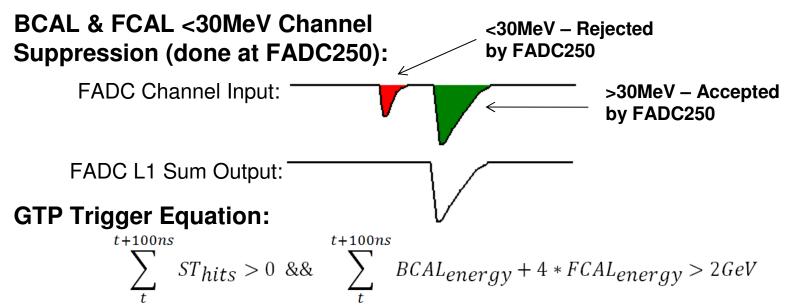

# 5.6 GlueX Example L1 Trigger

#### **Resulting L1 Acceptance Spectrum:**

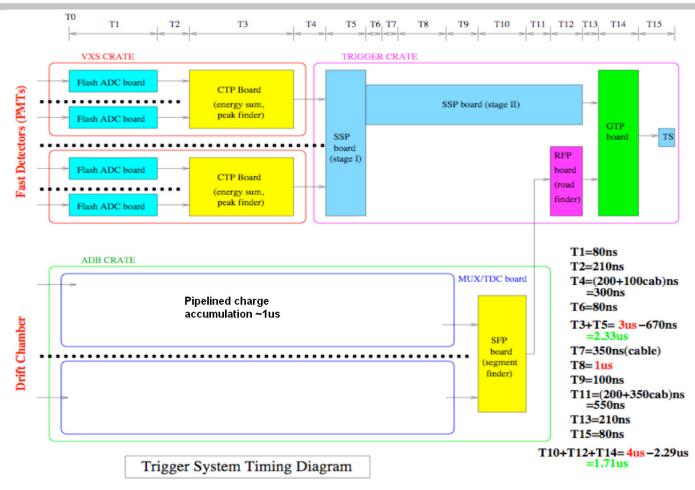

# **CLAS12 Trigger System Timing**

- -The drift chambers will also be part of L1 trigger system.

- Large trigger decision time allows for DC charge accumulation and advanced trigger logic.

### **GlueX Level 1 Timing**

2.3µs measured latency remaining latency FADC250 SSP **GTP** Global Trigger Crate Link: 64bits @ 125MHz Link: 32bits @ 125MHz BCal, FCal Mode: Link: 64bits @ 125MHz BCal, FCal Mode: BCal, FCal Mode: 19:0 ADCSum to 15:0 ADCSum to 39:20 ADCSum t, 22:0 ADCSum to 31:16 ADCSum t Link: 32bits @ 250MHz TOF, ST Mode: 55:23 ADCSum to 31:0 Triggers(31:0) TOF, ST, Tagger Mode: 8:0 TrackCount to 63:56 Unused 15:0 Hit Bits to 17:9 TrackCount to TOF, ST Mode: 31:16 Hit Bits 1, 39:18 Unused 11:0 TrackCount to Tagger Mode: 23:12 TrackCount t, 7:0 MinHit to 63:24 Unused t<sub>18</sub> 15:8 MaxHit t. Tagger Mode: TS Front-end Crate 23:16 MinHit t 7:0 MinHit to 31:24 MaxHit t<sub>s</sub> 15:8 MaxHit to 23:16 MinHit t, 39:32 Unused All Modes: 31:24 MaxHit to 47:40 Timestamo 63:32 Unused Link: 3bits @ 250MHz **Trigger Distribution** O Trigger 1 1 Trigger 2 2 Sync Crate Link: 16bits @ 62.5MHz 15:0 TriggerWord SD TI SD TD t<sub>13</sub>

2.3 $\mu$ s (measured) + 660ns (estimated) < 3 $\mu$ s!

660ns estimated

# IC & Hodoscope Trigger Logic

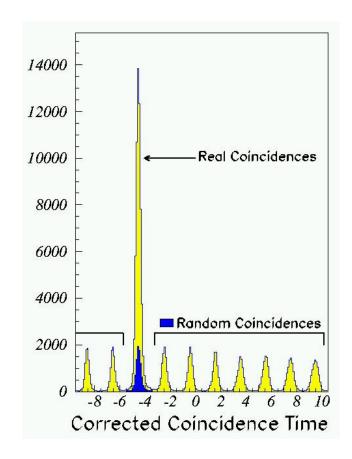

# **Event Trigger**

- A trigger condition will create a signal sent to all front-end modules to "readout" the event

- Timing resolution of event is resolved using high resolution TDCs and timing information received from ADC modules

- Triggered window/integration gate widths are much large than the bunch crossing time, so event data corresponds to multiple bunch crossings. Real event bunch crossing is easily distinguishable because of high resolution timing information

- CW beam creates random background which can be used to correct real event statistics

# **Global Trigger Logic**

### **GlueX Trigger Subsystems**

# **JLab Trigger Requirements**

- Minimal dead-time with random trigger rate:

- ~10-20kHz Hall B CLAS/CLAS12

- ~200kHz Hall D GlueX

- Trigger "continuously" evaluates detector against trigger criteria:

- every 4ns for 12GeV upgraded system

- every 5-15ns for current system

- Trigger hardware clock assumed to be asynchronous to bunch crossing/RF clock

- Trigger path has a fixed latency, though jitters with respect to the physics event ~= trigger clock

# 5.2 Existing CLAS Trigger